# **MICROSAR OS**

# **Technical Reference**

Version 1.7.0

| Authors | Anton Schmukel, Ivan Begert, Stefano Simoncelli, Torsten Schmidt, Da He, David Feuerstein, Michael Kock, Martin Schultheiß, Andreas Jehl |

|---------|------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                                                                                                                          |

| Status  | Released                                                                                                                                 |

## **Document Information**

## History

| Author                                | Date       | Version | Remarks                                                                                                                                                                                                                                                      |

|---------------------------------------|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Torsten Schmidt                       | 2016-04-27 | 1.0.0   | First release version                                                                                                                                                                                                                                        |

| Torsten Schmidt                       | 2016-05-18 | 1.0.1   | References to hardware manuals added. Revision work                                                                                                                                                                                                          |

| Torsten Schmidt                       | 2016-06-03 | 1.0.2   | Fix of ESCAN00089598                                                                                                                                                                                                                                         |

| Torsten Schmidt                       | 2016-06-20 | 1.1.0   | List of OS internal objects added.  Additional startup concept chapter added.  Chapter "Memory mapping concept" reworked.  Description of "generate callout stubs" feature added.                                                                            |

| Torsten Schmidt                       | 2016-07-05 | 1.1.1   | Chapter "Memory Mapping Concept" extended. IOC notification callback concept changed. HSI of RH850 family added. HSI of Power PC family added.                                                                                                               |

| Torsten Schmidt                       | 2016-07-19 | 1.1.2   | Chapter "Memory Mapping Concept" changed.<br>Hints for shorter compile times added.<br>Nesting behavior of OS hooks described.                                                                                                                               |

| Ivan Begert                           | 2016-08-11 | 1.1.3   | HSI of ARM family added.                                                                                                                                                                                                                                     |

| Torsten Schmidt                       | 2016-08-12 | 1.1.4   | Chapter "Memory Mapping Concept" extended. Chapter "Clear Pending Interrupt" extended. Chapter "RH850 Special Characteristics" extended.                                                                                                                     |

| Ivan Begert                           | 2016-08-18 | 1.1.5   | HSI of ARM Zynq UltraScale added.                                                                                                                                                                                                                            |

| Torsten Schmidt                       | 2016-08-30 | 1.1.6   | HSI of RH850 extended.                                                                                                                                                                                                                                       |

| Torsten Schmidt                       | 2016-08-31 | 1.1.7   | ORTI Debugging added. Timing Hook Macros reworked. Chapter "Memory Mapping Concept" changed. Chapter "Category 1 Interrupts" extended.                                                                                                                       |

| Stefano Simoncelli<br>Torsten Schmidt | 2016-09-15 | 1.1.8   | Chapter "Interrupt Source API" extended. HSI chapter for ARM extended                                                                                                                                                                                        |

| Torsten Schmidt                       | 2016-09-22 | 1.2.0   | VTT OS and Dual Target Concept added. Chapter ORTI Debugging extended.                                                                                                                                                                                       |

| Anton Schmukel<br>Da He               | 2016-10-14 | 1.3.0   | Ristrictions concerning API usage before StartOS() documented. Clarification concerning forcible termination and schedule tables added. Deviations in IOC added. Notes on mixed criticality systems added. Chapter "RH850 Special Characteristics" extended. |

| Torsten Schmidt                       | 2016-10-19 | 1.3.1   | Chapter "Configuration of X-Signals" added.                                                                                                                                                                                                                  |

|                                                                       |            |       | Chapter "Power PC Special Characteristics" extended. Correction of startup examples. Chapter "User include files" added. RH850 HSI extended. PPC HSI extended. Hardware Overview extended by RH850. |

|-----------------------------------------------------------------------|------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| David Feuerstein                                                      | 2016-11-03 | 1.4.0 | PPC HSI extended. Chapter ORTI Debugging extended.                                                                                                                                                  |

| Michael Kock                                                          | 2016-11-25 | 1.5.0 | Updated chapter Timing Hooks                                                                                                                                                                        |

| Martin Schultheiß                                                     | 2016-12-08 | 1.6.0 | PPC HSI extended. Updated characteristics of VTT OS.                                                                                                                                                |

| David Feuerstein<br>Andreas Jehl<br>Ivan Begert<br>Stefano Simoncelli | 2016-22-12 | 1.7.0 | Updated precautions in PreStartTask. Support new Power PC Derivative: PC580003 Support IAR compiler for ARM ARM Cortex-A HSI added                                                                  |

### **Reference Documents**

| No. | Source     | Title                                                                                                                                                                                                                         | Version                  |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| [1] | AUTOSAR    | Specification of Operating System  Document ID 034: AUTOSAR_SWS_OS                                                                                                                                                            | 4.2.1                    |

| [2] | OSEK/VDX   | OSEK/VDX Operating System Specification This document is available in PDF-format on the Internet at the OSEK/VDX homepage ( <a href="http://www.osek-vdx.org">http://www.osek-vdx.org</a> )                                   | 2.2.3                    |

| [3] | OSEK/VDX   | OSEK RunTime Interface (ORTI) Part A:<br>Language Specification.<br>This document is available in PDF-format on<br>the Internet at the OSEK/VDX homepage<br>( <a href="http://www.osek-vdx.org">http://www.osek-vdx.org</a> ) | 2.2                      |

| [4] | OSEK/VDX   | OSEK Run Time Interface (ORTI) Part B: OSEK Objects and Attributes This document is available in PDF-format on the Internet at the OSEK/VDX homepage (http://www.osek-vdx.org)                                                | 2.2                      |

| [5] | Lauterbach | ORTI Representation of SMP Systems (ORTI 2.3)                                                                                                                                                                                 | 4                        |

| [6] | Vector     | vVIRTUALtarget Technical Reference                                                                                                                                                                                            | See delivery information |

| [7] | Vector     | Startup with Vector and vVIRTUALtarget                                                                                                                                                                                        | See delivery information |

### Caution

We have configured the programs in accordance with your specifications in the questionnaire. Whereas the programs do support other configurations than the one specified in your questionnaire, Vector's release of the programs delivered to your company is expressly restricted to the configuration you have specified in the questionnaire.

### Contents

| 1 | Introd | luction         |                       |                                        | 16 |  |

|---|--------|-----------------|-----------------------|----------------------------------------|----|--|

|   | 1.1    | Architec        | ture Overvi           | ew                                     | 16 |  |

|   | 1.2    | Abstract        |                       |                                        | 17 |  |

|   | 1.3    | Characteristics |                       |                                        |    |  |

|   | 1.4    | Hardwai         | re Overview           | /                                      | 18 |  |

|   |        | 1.4.1           | TriCore A             | urix                                   | 19 |  |

|   |        | 1.4.2           | Power Po              | S                                      | 20 |  |

|   |        | 1.4.3           | ARM                   |                                        | 21 |  |

|   |        | 1.4.4           | RH850                 |                                        | 22 |  |

|   |        | 1.4.5           | VTT OS.               |                                        | 23 |  |

|   |        |                 | 1.4.5.1               | Characteristics of VTT OS              | 23 |  |

| 2 | Funct  | ional Des       | cription              |                                        | 24 |  |

|   | 2.1    | General         |                       |                                        | 24 |  |

|   | 2.2    | MICROS          | SAR OS De             | viations from AUTOSAR OS Specification | 24 |  |

|   |        | 2.2.1           | Generic [             | Deviation for API Functions            | 24 |  |

|   |        | 2.2.2           | Trusted F             | Function API Deviations                | 24 |  |

|   |        | 2.2.3           | Service F             | Protection Deviation                   | 25 |  |

|   |        | 2.2.4           | SyncSch               | eduleTable API Deviation               | 25 |  |

|   |        | 2.2.5           | CheckTa               | sk/ISRMemoryAccess API Deviation       | 25 |  |

|   |        | 2.2.6           | Interrupt             | API Deviation                          | 26 |  |

|   |        | 2.2.7           | Cross Co              | ore Getter APIs                        | 26 |  |

|   |        | 2.2.8           | IOC                   |                                        | 26 |  |

|   |        | 2.2.9           | Return va             | alue upon stack violation              | 27 |  |

|   |        | 2.2.10          | Forcible <sup>-</sup> | Termination of Applications            | 28 |  |

|   | 2.3    | Stack C         | oncept                |                                        | 29 |  |

|   |        | 2.3.1           | Task Stad             | ck Sharing                             | 31 |  |

|   |        |                 | 2.3.1.1               | Description                            | 31 |  |

|   |        |                 | 2.3.1.2               | Activation                             | 31 |  |

|   |        |                 | 2.3.1.3               | Usage                                  | 31 |  |

|   |        | 2.3.2           | ISR Stac              | k Sharing                              | 31 |  |

|   |        |                 | 2.3.2.1               | Description                            | 31 |  |

|   |        |                 | 2.3.2.2               | Activation                             | 31 |  |

|   |        |                 | 2.3.2.3               | Usage                                  | 32 |  |

|   |        | 2.3.3           | Stack Ch              | eck Strategy                           | 32 |  |

|   |        | 2.3.4           | Software              | Stack Check                            | 33 |  |

|   |        |                 | 2.3.4.1               | Description                            | 33 |  |

|   |        |                 | 2.3.4.2               | Activation                             | 33 |  |

|   |        |                 | 2.3.4.3               | Usage                                  | 33 |  |

|      | 2.3.5              | Stack Supe     | ervision by MPU                   | 34 |  |  |

|------|--------------------|----------------|-----------------------------------|----|--|--|

|      |                    | 2.3.5.1        | Description                       | 34 |  |  |

|      |                    | 2.3.5.2        | Activation                        | 34 |  |  |

|      |                    | 2.3.5.3        | Usage                             | 35 |  |  |

|      | 2.3.6              | Stack Usag     | ge Measurement                    | 37 |  |  |

|      |                    | 2.3.6.1        | Description                       | 37 |  |  |

|      |                    | 2.3.6.2        | Activation                        | 37 |  |  |

|      |                    | 2.3.6.3        | Usage                             | 37 |  |  |

| 2.4  | Interrupt          | Concept        |                                   | 38 |  |  |

|      | 2.4.1              | Interrupt H    | andling API                       | 38 |  |  |

|      |                    | 2.4.1.1        | Interrupt Handling in SC1 / SC3   | 38 |  |  |

|      |                    | 2.4.1.2        | Interrupt Handling in SC2 / SC4   | 39 |  |  |

|      | 2.4.2              | Interrupt Vo   | ector Table                       | 40 |  |  |

|      | 2.4.3              | Nesting of     | Category 2 Interrupts             | 40 |  |  |

|      |                    | 2.4.3.1        | Description                       | 40 |  |  |

|      |                    | 2.4.3.2        | Activation                        | 40 |  |  |

|      | 2.4.4              | Category 1     | Interrupts                        | 40 |  |  |

|      |                    | 2.4.4.1        | Implementation of Category 1 ISRs | 40 |  |  |

|      |                    | 2.4.4.2        | Nesting of Category 1 ISRs        | 41 |  |  |

|      |                    | 2.4.4.3        | Category 1 ISRs before StartOS    | 41 |  |  |

|      |                    | 2.4.4.4        | Notes on Category 1 ISRs          | 42 |  |  |

|      | 2.4.5              | Initializatio  | n of Interrupt Sources            | 43 |  |  |

|      | 2.4.6              | Unhandled      | Interrupts                        | 43 |  |  |

| 2.5  | Exception Concept  |                |                                   |    |  |  |

|      | 2.5.1              | Exception '    | Vector Table                      | 43 |  |  |

|      | 2.5.2              | Unhandled      | Exceptions                        | 43 |  |  |

| 2.6  | Timer Co           | oncept         |                                   | 44 |  |  |

|      | 2.6.1              | Description    | 1                                 | 44 |  |  |

|      | 2.6.2              | Activation.    |                                   | 44 |  |  |

|      | 2.6.3              | Usage          |                                   | 44 |  |  |

|      | 2.6.4 Dependencies |                |                                   |    |  |  |

| 2.7  | Periodic           | al Interrupt T | imer (PIT)                        | 45 |  |  |

|      | 2.7.1              | Description    | 1                                 | 45 |  |  |

|      | 2.7.2              | Activation.    |                                   | 45 |  |  |

| 2.8  | High Re            | solution Time  | er (HRT)                          | 46 |  |  |

|      | 2.8.1              | Description    | 1                                 | 46 |  |  |

|      | 2.8.2              | Activation.    |                                   | 46 |  |  |

| 2.9  | PIT vers           | us HRT         |                                   | 46 |  |  |

| 2.10 | Startup            | Concept        |                                   | 47 |  |  |

| 2.11 | Single C           | ore Startup    |                                   | 48 |  |  |

|      | 2.11.1             | Single Cor     | e Derivatives                     | 48 |  |  |

|      |                    |                |                                   |    |  |  |

|      | 2.11.2   | Multi Core                       | Derivatives                          | 49 |  |  |

|------|----------|----------------------------------|--------------------------------------|----|--|--|

|      |          | 2.11.2.1                         | Examples for SC1 / SC2 Systems       | 49 |  |  |

|      |          | 2.11.2.2                         | Examples for SC3 / SC4 Systems       | 50 |  |  |

| 2.12 | Multi Co | re Startup                       |                                      | 51 |  |  |

|      | 2.12.1   | Example f                        | or SC1 / SC2 Systems                 | 51 |  |  |

|      | 2.12.2   | Examples                         | for SC3 / SC4 systems                | 52 |  |  |

|      |          | 2.12.2.1                         | Only with AUTOSAR Cores              | 52 |  |  |

|      |          | 2.12.2.2                         | Mixed Core System                    | 53 |  |  |

| 2.13 | Error Ha | ındling                          |                                      | 54 |  |  |

| 2.14 | Error Re | porting                          |                                      | 54 |  |  |

|      | 2.14.1   | Extension                        | of Service IDs                       | 55 |  |  |

|      | 2.14.2   | Extension                        | of Error Codes                       | 55 |  |  |

|      | 2.14.3   | Detailed E                       | rror Codes                           | 56 |  |  |

| 2.15 | Multi Co | re Concepts                      | ·                                    | 57 |  |  |

|      | 2.15.1   | Schedulin                        | g and Dispatching                    | 57 |  |  |

|      | 2.15.2   | Multi Core                       | Data Concepts                        | 57 |  |  |

|      | 2.15.3   | X-Signals                        |                                      | 57 |  |  |

|      | 2.15.4   | Master / S                       | lave Core                            | 57 |  |  |

|      | 2.15.5   | Startup of a Multi Core System57 |                                      |    |  |  |

|      | 2.15.6   | Spinlocks                        |                                      | 57 |  |  |

|      | 2.15.7   | Cache                            |                                      | 58 |  |  |

|      | 2.15.8   | Shutdown                         |                                      | 58 |  |  |

|      |          | 2.15.8.1                         | Shutdown of one Core                 | 58 |  |  |

|      |          | 2.15.8.2                         | Shutdown of all Cores                | 58 |  |  |

|      |          | 2.15.8.3                         | Shutdown during Protection Violation | 58 |  |  |

| 2.16 | Debuggi  | ing Concept                      | S                                    |    |  |  |

|      | 2.16.1   | Descriptio                       | n                                    | 59 |  |  |

|      | 2.16.2   | Activation                       |                                      | 59 |  |  |

|      | 2.16.3   | ORTI Deb                         | ugging                               | 60 |  |  |

| 2.17 | Memory   | Protection                       |                                      | 62 |  |  |

|      | 2.17.1   | Usage of                         | the System MPU                       | 62 |  |  |

|      | 2.17.2   | Usage of                         | the Core MPUs                        | 62 |  |  |

|      | 2.17.3   | Configura                        | tion Aspects                         | 63 |  |  |

|      |          | 2.17.3.1                         | Static MPU Regions                   | 63 |  |  |

|      |          | 2.17.3.2                         | Dynamic MPU Regions                  |    |  |  |

|      |          | 2.17.3.3                         | Freedom from Interference            | 64 |  |  |

|      | 2.17.4   | Stack Mor                        | nitoring                             | 65 |  |  |

|      | 2.17.5   |                                  | Violation Handling                   |    |  |  |

|      | 2.17.6   |                                  | / Fast Core MPU Handling             |    |  |  |

|      | 2.17.7   | •                                | ended Configuration                  |    |  |  |

| 2.18 | Memorv   |                                  | ecks                                 |    |  |  |

|          | 2.18.1   | Descriptio    | n                                     | 67 |

|----------|----------|---------------|---------------------------------------|----|

|          | 2.18.2   | Activation    |                                       | 67 |

|          | 2.18.3   | Usage         |                                       | 67 |

|          | 2.18.4   | Depender      | ncies                                 | 67 |

| 2.19     | Timing F | Protection Co | oncept                                | 68 |

|          | 2.19.1   | Descriptio    | n                                     | 68 |

|          | 2.19.2   | Activation    |                                       | 69 |

|          | 2.19.3   | Usage         |                                       | 69 |

| 2.20     | IOC      |               |                                       | 70 |

|          | 2.20.1   | Descriptio    | n                                     | 70 |

|          | 2.20.2   | Unqeued       | (Last Is Best) Communication          | 70 |

|          |          | 2.20.2.1      | 1:1 Communication Variant             | 70 |

|          |          | 2.20.2.2      | N:1 Communication Variant             | 71 |

|          |          | 2.20.2.3      | N:M Communication Variant             | 71 |

|          | 2.20.3   | Queued C      | Communication                         | 71 |

|          | 2.20.4   | Notificatio   | n                                     | 71 |

|          | 2.20.5   | Particulari   | ties                                  | 72 |

|          |          | 2.20.5.1      | N:1 Queued Communication              | 72 |

|          |          | 2.20.5.2      | IOC Spinlocks                         | 72 |

|          |          | 2.20.5.3      | Notification                          | 73 |

| 2.21     | Trusted  | OS Applicat   | ions                                  | 74 |

|          | 2.21.1   | Trusted O     | S Applications with Memory Protection | 74 |

|          |          | 2.21.1.1      | Description                           | 74 |

|          |          | 2.21.1.2      | Activation                            | 74 |

|          |          | 2.21.1.3      | Dependencies                          | 74 |

|          | 2.21.2   | Trusted O     | S Applications in User Mode           | 74 |

|          |          | 2.21.2.1      | Description                           | 74 |

|          |          | 2.21.2.2      | Activation                            | 74 |

|          |          | 2.21.2.3      | Dependencies                          | 74 |

|          | 2.21.3   | Trusted F     | unctions                              | 75 |

| 2.22     | OS Hoo   | ks            |                                       | 76 |

|          | 2.22.1   | Runtime (     | Context                               | 76 |

|          | 2.22.2   | Nesting be    | ehavior                               | 76 |

|          | 2.22.3   | Hints         |                                       | 77 |

| <b>.</b> | 0 ::     | 00 5 4        |                                       |    |

|          | -        |               | es                                    |    |

| 3.1      | •        | •             | 3                                     |    |

|          | 3.1.1    | •             | n                                     |    |

|          | 3.1.2    |               |                                       |    |

|          | 3.1.3    | •             |                                       |    |

| 3.2      | Periphei | rai Access A  | Pl                                    | 79 |

|        | 3.2.1    | Descriptio     | n                                  | 79       |

|--------|----------|----------------|------------------------------------|----------|

|        | 3.2.2    | Activation     |                                    | 79       |

|        | 3.2.3    | Usage          |                                    | 79       |

|        | 3.2.4    | Depender       | ncies                              | 79       |

|        | 3.2.5    | Alternative    | es                                 | 79       |

|        | 3.2.6    | Common         | Use Cases                          | 79       |

| 3.3    | Trusted  | Function Ca    | ll Stubs                           | 80       |

|        | 3.3.1    | Descriptio     | n                                  | 80       |

|        | 3.3.2    | Activation     |                                    | 80       |

|        | 3.3.3    | Usage          |                                    | 80       |

|        | 3.3.4    | Depender       | ncies                              | 80       |

| 3.4    | Non-Tru  | sted Function  | ns (NTF)                           | 81       |

|        | 3.4.1    | Descriptio     | n                                  | 81       |

|        | 3.4.2    | Activation     |                                    | 81       |

|        | 3.4.3    | Usage          |                                    | 82       |

|        | 3.4.4    | Depender       | ncies                              | 82       |

| 3.5    | Interrup | t Source API   |                                    | 83       |

|        | 3.5.1    | Descriptio     | n                                  | 83       |

| 3.6    | Pre-Star | rt Task        |                                    | 84       |

|        | 3.6.1    | Descriptio     | n                                  | 84       |

|        | 3.6.2    | Activation     |                                    | 84       |

|        | 3.6.3    | Usage          |                                    | 84       |

|        | 3.6.4    | Depender       | ncies                              | 85       |

| 3.7    | X-Signa  | ls             |                                    | 86       |

|        | 3.7.1    | Descriptio     | n                                  | 86       |

|        |          | 3.7.1.1        | Notes on Synchronous X-Signals     | 89       |

|        |          | 3.7.1.2        | Notes on Mixed Criticality Systems | 89       |

|        | 3.7.2    | Activation     |                                    | 89       |

| 3.8    | Timing H | Hooks          |                                    | 90       |

|        | 3.8.1    | Descriptio     | n                                  | 90       |

|        | 3.8.2    | Activation     |                                    | 90       |

|        | 3.8.3    | Usage          |                                    | 90       |

| 3.9    | Kernel F | Panic          |                                    | 91       |

| 3.10   | Generat  | te callout stu | bs                                 | 92       |

|        | 3.10.1   | Descriptio     | n                                  | 92       |

|        | 3.10.2   | Activation     |                                    | 92       |

|        | 3.10.3   | Usage          |                                    | 92       |

| Intogr | ation    |                |                                    | 03       |

| 4.1    |          |                | on Assumptions                     |          |

| 7.1    | •        | Compile T      | ·                                  | 93<br>93 |

|        | - · ·    |                | 11.115.4                           |          |

| 4.2 | Hardwar | re Software | Interfaces (HSI)                            | 93  |

|-----|---------|-------------|---------------------------------------------|-----|

|     | 4.2.1   | TriCore A   | urix Family                                 | 94  |

|     |         | 4.2.1.1     | Context                                     | 94  |

|     |         | 4.2.1.2     | Core Registers                              | 94  |

|     |         | 4.2.1.3     | Interrupt Registers                         | 94  |

|     |         | 4.2.1.4     | GPT Registers                               | 95  |

|     |         | 4.2.1.5     | STM Registers                               | 95  |

|     |         | 4.2.1.6     | Aurix Special Characteristics               | 96  |

|     |         | 4.2.1.7     | PSW handling                                | 98  |

|     | 4.2.2   | RH850 Fa    | amily                                       | 99  |

|     |         | 4.2.2.1     | Context                                     | 99  |

|     |         | 4.2.2.2     | Core Registers                              | 100 |

|     |         | 4.2.2.3     | MPU Registers                               | 101 |

|     |         | 4.2.2.4     | INTC Registers                              | 101 |

|     |         | 4.2.2.5     | Inter Processor Interrupt Control Registers | 101 |

|     |         | 4.2.2.6     | Timer TAUJ Registers                        | 102 |

|     |         | 4.2.2.7     | Timer STM Registers                         | 104 |

|     |         | 4.2.2.8     | Timer OSTM Registers                        | 106 |

|     |         | 4.2.2.9     | RH850 Special Characteristics               | 107 |

|     |         | 4.2.2.10    | PSW Register Handling                       | 108 |

|     |         | 4.2.2.11    | Instructions                                | 108 |

|     |         | 4.2.2.12    | Exception and Interrupt Cause Address       | 108 |

|     | 4.2.3   | Power PC    | Family                                      | 109 |

|     |         | 4.2.3.1     | Context                                     | 109 |

|     |         | 4.2.3.2     | Core Registers                              | 109 |

|     |         | 4.2.3.3     | Interrupt Registers                         | 109 |

|     |         | 4.2.3.4     | PIT Registers                               | 110 |

|     |         | 4.2.3.5     | STM Registers                               | 110 |

|     |         | 4.2.3.6     | MPU Registers                               | 110 |

|     |         | 4.2.3.7     | SEMA4 Registers                             | 111 |

|     |         | 4.2.3.8     | Power PC Special Characteristics            | 111 |

|     |         | 4.2.3.9     | MSR Handling                                | 112 |

|     | 4.2.4   | ARM Fam     | nily                                        |     |

|     |         | 4.2.4.1     | Cortex-R derivatives                        | 113 |

|     |         | 4.2.4.2     | Cortex-A derivatives                        | 115 |

|     |         | 4.2.4.3     | ARM Special Characteristics                 | 115 |

| 4.3 | Memory  | Mapping C   | oncept                                      | 117 |

|     | 4.3.1   |             | MemMap Section Specifers                    |     |

|     |         | 4.3.1.1     | Usage of MemMap Macros                      | 120 |

|     |         | 4.3.1.2     | Resulting sections                          |     |

|     |         | 4.3.1.3     | Access Rights to Variable Sections          |     |

|                 | 4.3.2      | Link Sectio    | ns                                                     | 130  |

|-----------------|------------|----------------|--------------------------------------------------------|------|

|                 |            | 4.3.2.1        | Simple Linker Defines                                  | 131  |

|                 |            | 4.3.2.2        | Hierachical Linker Defines                             | 131  |

|                 |            | 4.3.2.3        | Selecting OS constants                                 | 132  |

|                 |            | 4.3.2.4        | Selecting OS variables                                 | 133  |

|                 |            | 4.3.2.5        | Selecting OS Barriers, Core Status and Trace variables | s134 |

|                 |            | 4.3.2.6        | Selecting OS Spinlocks                                 | 135  |

|                 |            | 4.3.2.7        | Selecting User Constant Sections                       | 136  |

|                 |            | 4.3.2.8        | Selecting User Variable Sections                       | 137  |

|                 | 4.3.3      | Section Sy     | mbols                                                  | 139  |

| 4.4             | Static Co  | de Analysis    |                                                        | 139  |

| 4.5             | Configura  | ation of X-Sig | gnals                                                  | 140  |

|                 | 4.5.1      | TriCore Au     | ix Family                                              | 140  |

|                 | 4.5.2      | RH850 Far      | nily                                                   | 140  |

|                 | 4.5.3      | Power PC       | Family                                                 | 141  |

|                 | 4.5.4      | ARM Famil      | y                                                      | 141  |

|                 | 4.5.5      | VTT OS         |                                                        | 141  |

| 4.6             | OS gener   | rated objects  | S                                                      | 141  |

|                 | 4.6.1      | System Ap      | olication                                              | 141  |

|                 | 4.6.2      | Idle Task      |                                                        | 142  |

|                 | 4.6.3      | Timer ISR.     |                                                        | 142  |

|                 | 4.6.4      | System Tin     | ner Counter                                            | 142  |

|                 | 4.6.5      | Timing Pro     | tection Counter                                        | 142  |

|                 | 4.6.6      | Timing prof    | ection ISR                                             | 142  |

|                 | 4.6.7      | Resource S     | Scheduler                                              | 143  |

|                 | 4.6.8      | J              | R                                                      |      |

|                 | 4.6.9      | -              | cks                                                    |      |

| 4.7             | VTT OS S   | •              |                                                        |      |

|                 | 4.7.1      | J              | on                                                     |      |

|                 | 4.7.2      |                | erface                                                 |      |

| 4.8             | User inclu | ude files      |                                                        | 145  |

| ADI Do          | carintian  |                |                                                        | 116  |

| 5.1             | =          |                | 1                                                      |      |

| J. I            | 5.1.1      |                | tions                                                  |      |

|                 | 5.1.2      |                | tions                                                  |      |

|                 | 5.1.3      |                | nctions                                                |      |

| 5.2             |            |                | TICUOTIS                                               |      |

| 5.2             |            |                | ns (NTF)                                               |      |

| 5.4             |            |                | is (IVII )                                             |      |

| ∪. <del>⊤</del> | 5.4.1      |                | errupt Source                                          |      |

|                 | J.T. I     | שונו טוטטטוט   | Strapt Course                                          | 100  |

|        | 5.4.2     | Enable Inf  | terrupt Source             | 156 |

|--------|-----------|-------------|----------------------------|-----|

|        | 5.4.3     | Clear Pen   | ding Interrupt             | 157 |

|        | 5.4.4     | Check Inte  | errupt Source Enabled      | 158 |

|        | 5.4.5     | Check Into  | errupt Pending             | 159 |

| 5.5    | Detailed  | Error API   |                            | 160 |

|        | 5.5.1     | Get detail  | ed Error                   | 160 |

|        | 5.5.2     | Unhandle    | d Interrupt Requests       | 161 |

|        | 5.5.3     | Unhandle    | d Exception Requests       | 162 |

| 5.6    | Stack U   | sage API    |                            | 163 |

| 5.7    | RTE Inte  | errupt API  |                            | 164 |

| 5.8    | Time Co   | nversion Ma | acros                      | 165 |

|        | 5.8.1     | Convert fr  | om Time into Counter Ticks | 165 |

|        | 5.8.2     | Convert fr  | om Counter Ticks into Time | 165 |

| 5.9    | Access    | Check API   |                            | 166 |

|        | 5.9.1     | Check ISF   | R Memory Access            | 166 |

|        | 5.9.2     | Check Tas   | sk Memory Access           | 167 |

| 5.10   | OS Initia | alization   |                            | 168 |

| 5.11   | Timing F  | looks       |                            | 170 |

|        | 5.11.1    | Timing Ho   | oks for Activation         | 170 |

|        |           | 5.11.1.1    | Task Activation            | 170 |

|        |           | 5.11.1.2    | Set Event                  | 171 |

|        | 5.11.2    | Timing Ho   | ook for Context Switch     | 172 |

|        | 5.11.3    | Timing Ho   | oks for Locking Purposes   | 173 |

|        |           | 5.11.3.1    | Get Resource               | 173 |

|        |           | 5.11.3.2    | Release Resource           | 173 |

|        |           | 5.11.3.3    | Request Spinlock           | 174 |

|        |           | 5.11.3.4    | Request Internal Spinlock  | 174 |

|        |           | 5.11.3.5    | Get Spinlock               | 175 |

|        |           | 5.11.3.6    | Get Internal Spinlock      | 175 |

|        |           | 5.11.3.7    | Release Spinlock           | 176 |

|        |           | 5.11.3.8    | Release Internal Spinlock  | 176 |

|        |           | 5.11.3.9    | Disable Interrupts         | 177 |

|        |           | 5.11.3.10   | Enable Interrupts          | 178 |

| 5.12   | PanicHo   | ok          |                            | 179 |

| 5.13   | Calling ( | Context Ove | rview                      | 180 |

| Config | guration  |             |                            | 181 |

| Gloss  | ary       |             |                            | 182 |

| Conta  | ct        |             |                            | 183 |

7

### Illustrations

| Figure 1-1 | AUTOSAR Architecture Overview                            | . 16 |

|------------|----------------------------------------------------------|------|

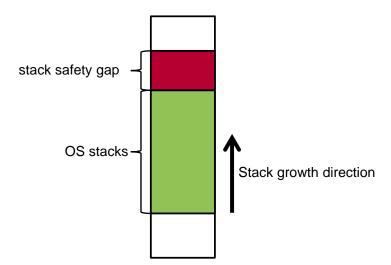

| Figure 2-1 | Stack Safety Gap                                         | . 35 |

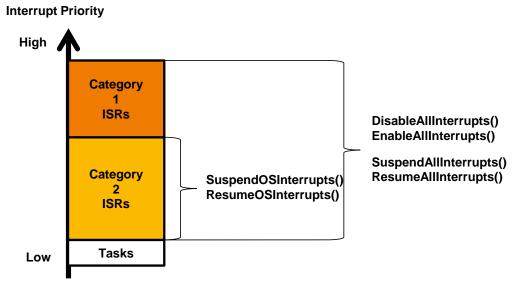

| Figure 2-2 | Interrupt APIs in SC1 / SC3                              | . 38 |

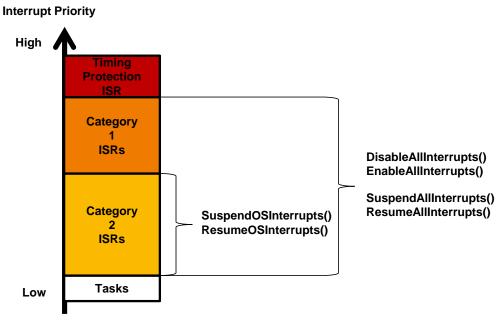

| Figure 2-3 | Interrupt API in SC2 / SC4                               |      |

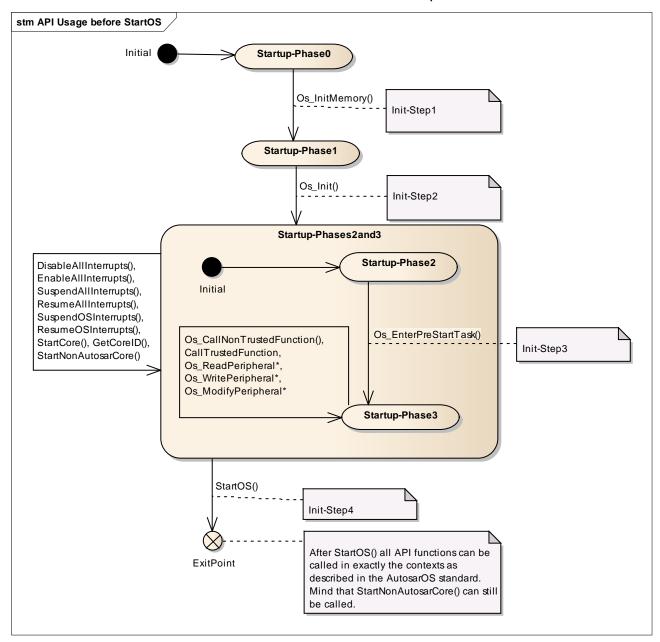

| Figure 2-4 | API functions during startup                             | . 47 |

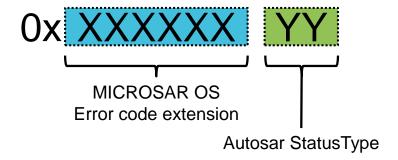

| Figure 2-5 | MICROSAR OS Detailed Error Code                          |      |

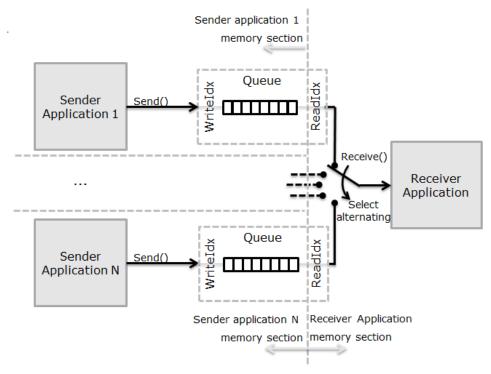

| Figure 2-6 | N:1 Multiple Sender Queues                               | . 72 |

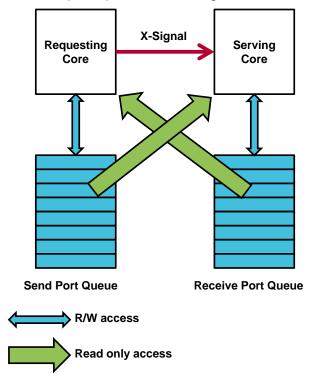

| Figure 3-1 | X-Signal                                                 |      |

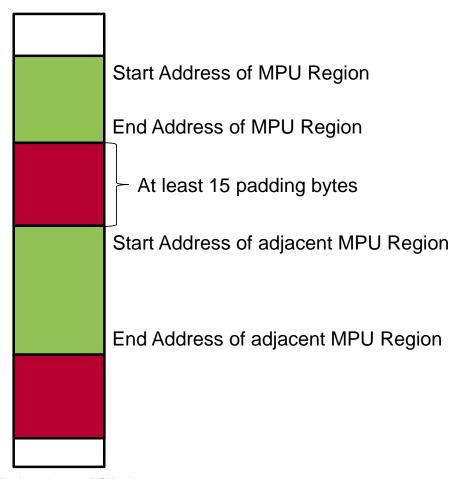

| Figure 4-1 | Padding bytes between MPU regions                        |      |

| · ·        | 0 ,                                                      |      |

| Tables     |                                                          |      |

| Table 1-1  | MICROSAR OS Characteristics                              | 17   |

| Table 1-2  | Supported TriCore Aurix Hardware                         |      |

| Table 1-3  | Supported TriCore Aurix Compilers                        |      |

| Table 1-4  | Supported Power PC Hardware                              |      |

| Table 1-5  | Supported Power PC compilers                             |      |

| Table 1-5  | Supported ARM Hardware                                   |      |

| Table 1-0  | Supported ARM compilers                                  |      |

| Table 1-7  | Supported RH850 Hardware                                 |      |

| Table 1-9  | Supported RH850 Compilers                                |      |

| Table 1-10 | VTT OS characteristics                                   |      |

| Table 2-1  | MICROSAR OS Stack Types                                  |      |

| Table 2-2  | Stack Check Patterns                                     |      |

| Table 2-3  | PIT versus HRT                                           |      |

| Table 2-4  | Types of OS Errors                                       |      |

| Table 2-5  | Extension of Error Codes                                 |      |

| Table 2-6  | Recommended Configuration MPU Access Rights              |      |

| Table 3-1  | Differences of OS and Optimized Spinlocks                |      |

| Table 3-2  | Comparison between Synchronous and Asynchronous X-Signal |      |

| Table 3-3  | Priority of X-Signal receiver ISR                        |      |

| Table 4-1  | Provided MemMap Section Specifiers                       |      |

| Table 4-2  | MemMap Code Sections Descriptions                        |      |

| Table 4-3  | MemMap Const Sections Descriptions                       |      |

| Table 4-4  | MemMap Variable Sections Descriptions                    |      |

| Table 4-5  | Recommended Section Access Rights                        |      |

| Table 4-6  | List of Generated Linker Command Files                   | 130  |

| Table 4-7  | OS constants linker define group                         | 132  |

| Table 4-8  | OS variables linker define group                         | 133  |

| Table 4-9  | OS Barriers and Core status linker define group          | 134  |

| Table 4-10 | User constants linker define group                       |      |

| Table 4-11 | User variables linker define group                       | 137  |

| Table 5-1  | Read Peripheral API                                      | 147  |

| Table 5-2  | Write Peripheral APIs                                    |      |

| Table 5-3  | Bitmask Peripheral API                                   |      |

| Table 5-4  | API Service Os_EnterPreStartTask                         |      |

| Table 5-5  | Call Non-Trusted Function API                            |      |

| Table 5-6  | API Service Os_DisableInterruptSource                    |      |

| Table 5-7  | API Service Os_EnableInterruptSource                     |      |

| Table 5-8  | API Service Os_ClearPendingInterrupt                     |      |

| Table 5-9  | API Service Os_IsInterruptSourceEnabled                  | 158  |

| Table 5-10 | API Service Os_IsInterruptPending            | 159 |

|------------|----------------------------------------------|-----|

| Table 5-11 | API Service Os_GetDetailedError              | 160 |

| Table 5-12 | API Service Os_GetUnhandledIrq               | 161 |

| Table 5-13 | API Service Os_GetUnhandledExc               | 162 |

| Table 5-14 | Overview: Stack Usage Functions              | 163 |

| Table 5-15 | Conversion Macros from Time to Counter Ticks | 165 |

| Table 5-16 | Conversion Macros from Counter Ticks to Time | 165 |

| Table 5-17 | API Service CheckISRMemoryAccess             | 166 |

| Table 5-18 | API Service CheckTaskMemoryAccess            | 167 |

| Table 5-19 | API Service Os_Init                          | 168 |

| Table 5-20 | API Service Os_InitMemory                    | 169 |

| Table 5-21 | Calling Context Overview                     | 180 |

|            |                                              |     |

#### 1 Introduction

This document describes the usage and functions of "MICROSAR OS", an operating system which implements the AUTOSAR BSW module "OS" as specified in [1].

This documentation assumes that the reader is familiar with both the OSEK OS<sup>1</sup> specification and the AUTOSAR OS specification.

#### 1.1 **Architecture Overview**

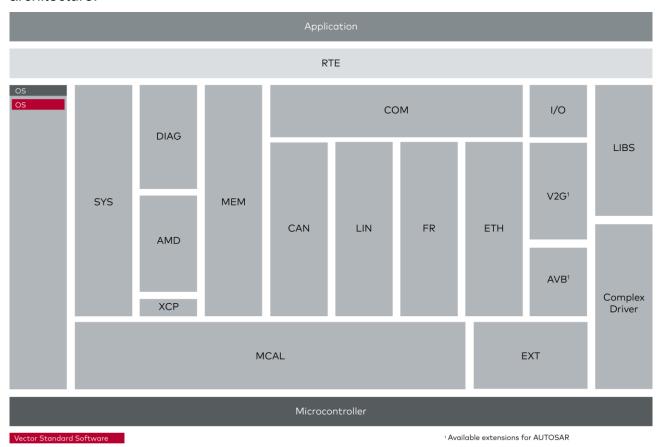

The following figure shows the location of the OS module within the AUTOSAR architecture.

Figure 1-1 AUTOSAR Architecture Overview

<sup>1</sup> OSEK is a registered trademark of Continental Automotive GmbH (until 2007: Siemens AG)

© 2016 Vector Informatik GmbH Version 1.7.0 16

#### 1.2 Abstract

The MICROSAR OS operating system is a real time operating system, which was specified for the usage in electronic control.

As a requirement, there is no dynamic creation of new tasks at runtime; all tasks have to be defined before compilation (pre-compile configuration variant).

The OS has no dynamic memory management and there is no shell for the control of tasks by hand.

Typically the source and configuration files of the operating system and the application source files are compiled and linked together to one executable file, which is loaded into an emulator or is burned into an EPROM or Flash EEPROM.

### 1.3 Characteristics

MICROSAR OS has the following characteristics:

| Supported Scalability Classes | SC1, SC2, SC3, SC4 (as described in [1]) |

|-------------------------------|------------------------------------------|

| Single Core ECUs              | Supported                                |

| Multi Core ECUs               | Supported                                |

| IOC                           | Supported                                |

Table 1-1 MICROSAR OS Characteristics

MICROSAR OS supports various different processor families of different vendors in conjunction with multiple compilers.

The availability for a particular processor in conjunction with a specific compiler can be queried from Vector Informatik.

#### 1.4 Hardware Overview

The following table summarizes information about MICROSAR OS. It gives detailed information about the derivatives and compilers. As very important information the documentations of the hardware manufacturers are listed. MICROSAR OS is based upon these documents in the given version.

### **Table Rows**

- > Compiler: List of Compilers MICROSAR OS is working with.

- **Derivative**: This can be a single information or a list of derivatives, MICROSAR OS can be used on.

- Hardware Manufacturer Document Name: List of hardware documentation MICROSAR OS is based on.

- **Document Version**: To be able to reference to this hardware documentation its version is very important.

### 1.4.1 TriCore Aurix

| Derivative     | Hardware Manufacturer Document Name                                     | Document<br>Version |

|----------------|-------------------------------------------------------------------------|---------------------|

| TC21x          | User Manual: tc23x_tc22x_tc21x_um_v1.1.pdf                              | V1.1                |

| TC22x<br>TC23x | Errata Sheet: TC22x_TC21x_AB_Errata_Sheet_v1_2_03804A.pdf               | V1.2                |

| TC24x          | Target Specification: tc24x_ts_v2.0_OPEN_MARKET.pdf                     | V2.0                |

| TC26x          | User Manual: V1.3 tc26xB um v1.3. usermanual rev1v3.pdf                 |                     |

|                | Errata Sheet:<br>TC26x_BB_Errata_Sheet_rev1v2_03989A_2016-04-18.pdf     | V1.2                |

| TC27x          | User Manual: tc27xD_um_v2.2_UserManual_rev2v2_2014-12.pdf               | V2.2                |

|                | Errata Sheet: TC27x_BC_Errata_Sheet_rev1v5_2015_09_16.pdf               | V1.5                |

| TC29x          | User Manual: tc29xB_um_v1.3TC29x_B-Step_User_Manual_rev_1v3_2014_12.pdf | V1.3                |

|                | Errata Sheet: TC29x_BA_Errata_Sheet_v1_0.pdf                            | V1.0                |

Table 1-2 Supported TriCore Aurix Hardware

| Tasking       | v4.2r2   |

|---------------|----------|

| HighTec (GNU) | V4.6.3.0 |

Table 1-3 Supported TriCore Aurix Compilers

### 1.4.2 Power PC

| Derivative | Hardware Manufacturer Document Name               | Document<br>Version  |

|------------|---------------------------------------------------|----------------------|

| MPC574xBD  | Freescale Semiconductor MPC5746C Reference Manual | Rev. 2.1,<br>06/2015 |

| MPC574xC1  | Freescale Semiconductor MPC5746C Reference Manual | Rev. 2.1,<br>06/2015 |

| MPC574xC2  | NXP MPC5748G Reference Manual                     | Rev. 4, 07/2015      |

| MPC574xG   | NXP MPC5748G Reference Manual                     | Rev. 4, 07/2015      |

|            | NXP Safety Manual for MPC5748G                    | Rev. 2, 01/2016      |

| MPC574xK   | ST SPC574Kxx<br>Reference Manual                  | Rev. 5, 08/2015      |

| MPC574xM   | Freescale Semiconductor MPC5746M Reference Manual | Rev. 5.1,<br>04/2014 |

| MPC574xP   | Freescale Semiconductor MPC5744P Reference Manual | Rev. 5.1,<br>02/2015 |

|            | NXP Safety Manual for MPC5744P                    | Rev. 3, 06/2014      |

| MPC574xR   | NXP MPC5746R<br>Reference Manual                  | Rev. 6, 03/2016      |

| MPC577xK   | Freescale Semiconductor MPC5775K Reference Manual | Rev. 4, 12/2015      |

| MPC577xM   | NXP MPC5777M<br>Reference Manual                  | Rev. 4, 04/2015      |

| MPC577xN   | Freescale Semiconductor MPC5774N Reference Manual | Rev. 2, 02/2014      |

| PC580003   | Freescale Semiconductor PC580003 Reference Manual | Rev. 2, 05/2014      |

| SPC58ECxx  | ST SPC584Cx/SPC58ECx<br>Reference Manual          | Rev. 1, 10/2015      |

| SPC58EGxx  | ST SPC58NE84x/SPC58xG84x Reference Manual         | Rev. 2, 02/2016      |

| SPC58NGxx  | ST SPC58NE84x/SPC58xG84x Reference Manual         | Rev. 2, 02/2016      |

| SPC582Bxx  | ST SPC582Bx<br>Reference Manual                   | Rev. 1, 08/2015      |

| SPC584Bxx  | ST SPC584Cx/SPC58ECx<br>Reference Manual          | Rev. 1, 10/2015      |

| SPC584Cxx  | ST SPC584Cx/SPC58ECx<br>Reference Manual          | Rev. 1, 10/2015      |

| SPC584Gxx  | ST SPC58NE84x/SPC58xG84x Reference Manual         | Rev. 2, 02/2016      |

Table 1-4 Supported Power PC Hardware

| Windriver DiabData | 5.9.4.x  |

|--------------------|----------|

| Green Hills (GHS)  | 2014.1.6 |

Table 1-5 Supported Power PC compilers

### 1.4.3 ARM

| Derivative | Hardware Manufacturer Document Name                      | Document<br>Version  |

|------------|----------------------------------------------------------|----------------------|

| S6J32xx    | Cypress S6J3200 Series Hardware Manual                   | Rev. 4.0,<br>09/2015 |

| ZUxxx      | XILINX Zynq UltraScale+ MPSoc Technical Reference Manual | v1.2, 06/2016        |

| iMX6xx     | i.MX 6Dual/6Quad Applications Processor Reference Manual | Rev. 3,<br>07/2015   |

Table 1-6 Supported ARM Hardware

| Green Hills (GHS) | 2013.5.4 |

|-------------------|----------|

| IAR               | V7.50.1  |

Table 1-7 Supported ARM compilers

### 1.4.4 RH850

| Derivative Family      | Hardware Manufacturer Document Name         | Document Version   |

|------------------------|---------------------------------------------|--------------------|

| RH850 C1M<br>RH850 C1H | RH850/C1x User's Manual: Hardware           | Rev.1.00 Mar 2015  |

| RH850 D1x              | RH850/D1L/D1M Group User's Manual: Hardware | Rev.2.01 Aug 2016  |

| RH850 E1x FCC2         | RH850/E1x-FCC2 User's Manual: Hardware      | Rev.0.50 Apr 2015  |

| RH850 E1x FCC1         | RH850/E1x-FCC1 User's Manual: Hardware      | Rev.0.50 Jul 2014  |

| RH850 E1L              | RH850/E1L User's Manual: Hardware           | Rev.1.10 Apr 2016  |

| RH850 E1M              | RH850/E1M-S User's Manual: Hardware         | Rev.1.10 Apr 2016  |

| RH850 F1H              | RH850/F1H Group User's Manual: Hardware     | Rev.1.12 May 2016  |

| RH850 F1L              | RH850/F1L Group User's Manual: Hardware     | Rev.1.33 Apr 2016  |

| RH850 F1K              | RH850/F1K Group User's Manual: Hardware     | Rev.1.00 Jun 2016  |

| RH850 F1M              | RH850/F1M Group User's Manual: Hardware     | Rev.1.03 May 2016  |

| RH850 P1HC             | RH850/P1x-C Group User's Manual: Hardware   | Rev.1.10 Jul 2016  |

| RH850 P1MC             | RH850/P1x-C Group User's Manual: Hardware   | Rev.1.10 Jul 2016  |

| RH850 P1M              | RH850/P1x Group User's Manual: Hardware     | Rev.1.00 Jul, 2015 |

| RH850 R1L              | RH850/R1x Group User's Manual: Hardware     | Rev.1.31 Jun 2016  |

| G3K Core               | RH850G3K User's Manual: Software            | Rev.1.20 Apr 2016  |

| G3KH Core              | RH850G3KH User's Manual: Software           | Rev.1.10 Jul 2016  |

| G3M Core               | RH850G3M User's Manual: Software            | Rev.1.30 Jun 2016  |

| G3MH Core              | RH850G3MH User's Manual: Software           | Rev.1.00 Mar 2015  |

Table 1-8 Supported RH850 Hardware

| Green Hills (GHS) | V6.1.4 2013.5.5 |

|-------------------|-----------------|

| ( /               | V6.1.6 2015.1.5 |

Table 1-9 Supported RH850 Compilers

### 1.4.5 VTT OS

VTT OS stands for "vVIRTUALtarget Operating System". It runs within Vectors CANoe development tool.

Vectors CANoe is capable of simulating an entire ECU network. Within such a simulated network the OS of each ECU can be simulated.

This is useful in early ECU development phases when no real hardware is available yet. Application development can be started at once.

The VTT OS behaves as regular AUTOSAR OS. All OS objects (e.g. tasks or ISRs) are simulated.

The VTT system is described in [6].

#### 1.4.5.1 **Characteristics of VTT OS**

| Supported Scalability Classes         | SC1, SC2                                                                                           |

|---------------------------------------|----------------------------------------------------------------------------------------------------|

| Single Core ECUs                      | Supported                                                                                          |

| Multi Core ECUs                       | Up to 32 cores are supported                                                                       |

| IOC                                   | Supported                                                                                          |

| Number of Simulated Interrupt Sources | Up to 10000                                                                                        |

| Simulated Interrupt Levels            | VTT OS allows interrupt levels from 1 200 Whereas 1 is the lowest priority and 200 is the highest. |

| Memory Protection                     | Not supported <sup>2</sup>                                                                         |

| Stack Protection                      | Not supported                                                                                      |

| Stack Usage Measurement               | Not supported                                                                                      |

| Stack Sharing                         | Not supported                                                                                      |

Table 1-10 VTT OS characteristics

© 2016 Vector Informatik GmbH Version 1.7.0 23 based on template version 6.0.1

<sup>&</sup>lt;sup>2</sup> The memory protection can be configured. However the actual protection mechanism is not executed.

### **2 Functional Description**

### 2.1 General

The MICROSAR OS basically implements the OS according to the AUTOSAR OS standard referred in [1].

It is possible that MICROSAR OS deviates from specified AUTOSAR OS behavior. All deviations from the standard are listed in the chapters hereafter.

On the other hand MICROSAR OS extends the AUTOSAR OS standard with numerous functions. These extensions in function are described in detail in chapter 2.21.1.

### 2.2 MICROSAR OS Deviations from AUTOSAR OS Specification

### 2.2.1 Generic Deviation for API Functions

| Specified Behavior           | There are some API functions which are only available within specific scalability classes (e.g. TerminateApplication() in SC3 and SC4 only).                                    |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Deviation Description</b> | Within the MICROSAR OS all API functions are always available.                                                                                                                  |

| Deviation Reason             | The static OS code gets more simplified for better maintainability (less pre-processor statements are necessary).  Modern toolchains will remove unused function automatically. |

### 2.2.2 Trusted Function API Deviations

| Specified Behavior    | The Operating System shall not schedule any other Tasks which belong to the same OS-Application as the non-trusted caller of the service. Also interrupts of Category 2 which belong to the same OS-Application shall be disabled during the execution of the service. |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deviation Description | In MICROSAR OS the re-scheduling of tasks in this particular case is not suppressed. The selective disabling of category 2 ISRs is also not done.                                                                                                                      |

| Deviation Reason      | For a better runtime performance during trusted function calls the specified behavior is not implemented in MICROSAR OS.  Data consistency problems can be solved in a more efficient way by using the OS interrupt API and/or OS resource API.                        |

| Specified Behavior    | All specified OS APIs should be called with interrupts enabled.  In case CallTrustedFunction() API is called with disabled interrupts it                                                             |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | returns the status code E_OS_DISABLEDINT.                                                                                                                                                            |

| Deviation Description | In MICROSAR OS this limitation does not exist. It is allowed to call CallTrustedFunction() API with disabled interrupts. There is no error check. The return value E_OS_DISABLEDINT is not possible. |

| Deviation Reason      | It offers the possibility to call CallTrustedFunction() API where interrupts may be disabled. This is more convenient and reasonable.                                                                |

### 2.2.3 Service Protection Deviation

| Specified Behavior    | If an invalid address (address is not writable by this OS-Application) is passed as an out-parameter to an Operating System service, the Operating System module shall return the status code E_OS_ILLEGAL_ADDRESS.                                                                            |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deviation Description | The validity of out-parameters is checked automatically by the MPU. Write accesses to such parameters are always done with the accessing rights of the caller of the OS service.  If the address is invalid a MPU exception is raised.  The return value E_OS_ILLEGAL_ADDRESS is not possible. |

| Deviation Reason      | Hardware checks by the MPU are much more performant than software memory checks.                                                                                                                                                                                                               |

## 2.2.4 SyncScheduleTable API Deviation

| Specified Behavior    | All specified OS APIs should be called with interrupts enabled. In case SyncScheduleTable() is called with disabled interrupts it returns the status code E_OS_DISABLEDINT.                    |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deviation Description | In MICROSAR OS this limitation does not exist. It is allowed to call SyncScheduleTable() with disabled interrupts. There is no error check. The return value E_OS_DISABLEDINT is not possible. |

| Deviation Reason      | It offers the possibility to call SyncScheduleTable() where interrupts may be disabled. This is more convenient and reasonable.                                                                |

### 2.2.5 CheckTask/ISRMemoryAccess API Deviation

| Specified Behavior    | All specified OS APIs should be called with interrupts enabled. In case one of these APIs is called with disabled interrupts it issues the error E_OS_DISABLEDINT.                             |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deviation Description | In MICROSAR OS this limitation does not exist. It is allowed to call these API functions with disabled interrupts. There is no error check. The return value E_OS_DISABLEDINT is not possible. |

| Deviation Reason      | It offers the possibility to call these functions e.g. from hardware drivers where interrupts may be disabled. This is more convenient and reasonable.                                         |

| Specified Behavior    | The API functions CheckTask/ISRMemoryAccess() are only allowed within specific OS call contexts (Task/Cat2 ISR/ErrorHook/ProtectionHook) In case one of these APIs is called within the wrong OS call context it issues the error E_OS_CALLEVEL. |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deviation Description | In MICROSAR OS In MICROSAR OS this limitation does not exist. It is allowed to call these API functions from all OS contexts. The return value E_OS_CALLEVEL is not possible.                                                                    |

| Deviation Reason      | Practically it is more reasonable to allow these APIs in all OS runtime contexts.                                                                                                                                                                |

## 2.2.6 Interrupt API Deviation

| Specified Behavior    | The API functions SuspendOSInterrupts() and ResumeOSInterrupts() are allowed within a category 1 ISR                                                                                                                     |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deviation Description | In MICROSAR OS it is not allowed to use SuspendOSInterrupts() and ResumeOSInterrupts() within a category 1 ISR.                                                                                                          |

| Deviation Reason      | The function SuspendOSInterrupts() lowers the current interrupt level when used in a category 1 ISR. This may lead to data inconsistencies if another category 1 ISR occurs.  Therefore those functions are not allowed. |

### 2.2.7 Cross Core Getter APIs

| Specified Behavior           | All getter APIs (e.g. GetTaskID()) may be called cross core within hooks and non nestable category 2 ISRs.                                 |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Deviation Description</b> | MICROSAR OS does not allow usage of those functions within OS Hooks and non-nestable category 2 ISRs.                                      |

| Deviation Reason             | Deadlock avoidance due to disabled interrupts in case that there are two simultaneous concurrent usages of those APIs from multiple cores. |

### 2.2.8 IOC

| Specified Behavior    | locSend/locWrite APIs have an IN parameter. The parameter will be passed by value for primitive data elements and by reference for all other types. The data type is configured in "OslocDataTypeRef".                                                                                                                       |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deviation Description | The configurator does not evaluate information in "OslocDataTypeRef". Instead it evaluates the parameter "OslocDataType". Primitive data types are passed by value. The configurator identifies the following strings as primitive data types: "uint8", "uint16" and "uint32". All other data types are passed by reference. |

| Deviation Reason      | Usage of "OslocDataType" reduces dependencies and complexity of the OS configurator.                                                                                                                                                                                                                                         |

## 2.2.9 Return value upon stack violation

| Specified Behavior    | If a stack fault is detected by stack monitoring AND no ProtectionHook is configured, the Operating System module shall call the ShutdownOS() service with the status E_OS_STACKFAULT.                                                              |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deviation Description | Within a SC3 / SC4 system with MPU stack supervision: If a stack fault is detected by stack monitoring AND no ProtectionHook is configured, the Operating System module shall call the ShutdownOS() service with the status E_OS_PROTECTION_MEMORY. |

| Deviation Reason      | With Hardware stack supervision MICROSAR OS is not possible to distinguish between stack violation and other memory violation                                                                                                                       |

| Specified Behavior    | If a stack fault is detected by stack monitoring AND a ProtectionHook is configured the Operating System module shall call the ProtectionHook() with the status E_OS_STACKFAULT.                                                              |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deviation Description | Within a SC3 / SC4 system with MPU stack supervision: If a stack fault is detected by stack monitoring AND a ProtectionHook is configured the Operating System module shall call the ProtectionHook() with the status E_OS_PROTECTION_MEMORY. |

| Deviation Reason      | With Hardware stack supervision MICROSAR OS is not possible to distinguish between stack violation and other memory violation                                                                                                                 |

## 2.2.10 Forcible Termination of Applications

| Specified Behavior    | AUTOSAR does not specify the handling of "next" schedule tables in case of forcible termination of applications.                                                                                                                             |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deviation Description | Use case: An application has a running schedule table which itself has a nexted schedule table of a foreign application. The foreign application is forcibly terminated.  The OS removes the "next" request from the running schedule table. |

| Deviation Reason      | Clarification of behavior. Impact on other applications should be minimal, therefore the current schedule table is not stopped. This is different to the behavior of StopScheduleTable().                                                    |

| Specified Behavior    | AUTOSAR does not specify the handling of "next" schedule tables in case of forcible termination of applications.                                                                                                                                                                                                                                          |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deviation Description | Use case: An application has a running schedule table which itself has a nexted schedule table of a foreign application. The first application is forcibly terminated.  The OS stops the current schedule table of the terminated application. and removes the "next" request. As a result it does not switch to the "next" schedule table of the foreign |

| Deviation Reason      | application.  Clarification of behavior.  Impact on other applications should be minimal. The described behavior is identical to the behavior of StopScheduleTable().                                                                                                                                                                                     |

### 2.3 Stack Concept

MICROSAR OS implements a specific stack concept.

It defines different stacks which may be used by stack consumers (runtime contexts). Whereas not all stacks may be used by all consumers.

The following table gives an overview.

| Stack Type                 | Multiplicity | Possible Stack Consumers                                                                                                                                                                                                            |

|----------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Kernel stack               | 1 per core   | <ul><li>OS memory exception handling</li><li>Os_PanicHook()</li></ul>                                                                                                                                                               |

| Protection stack           | 01 per core  | <ul><li>&gt; ProtectionHook()</li><li>&gt; OS API calls</li><li>&gt; Os_PanicHook()</li></ul>                                                                                                                                       |

| Error stack                | 01 per core  | <ul> <li>ErrorHooks (global and OS-application specific)</li> <li>OS API calls</li> <li>Category 1 ISRs</li> <li>Os_PanicHook()</li> </ul>                                                                                          |

| Shutdown stack             | 01 per core  | <ul> <li>ShutdownHooks (global and OS-application specific)</li> <li>OS API calls</li> <li>Os_PanicHook()</li> </ul>                                                                                                                |