## V850/850E ICE SERVER Reference Manual

Document #10952 Rev.9.15 Copyright © 2017 by

### Advanced Data Controls Corp.

All rights reserved.

#### **DISCLAIMER**

GREEN HILLS SOFTWARE, INC. AND ADVANCED DATA CONTROLS CORP. MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE CONTENTS HEREOF AND SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE.

Further, Green Hills Software, Inc. and Advanced Data Controls Corp. reserves the right to revise this publication and to make changes from time to time in the content hereof without obligation of Green Hills Software, Inc. and Advanced Data Controls Corp. to notify any person of such revision or changes.

Copyright © 1983-2017 by Green Hills Software, Inc. and Advanced Data Controls Corp. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without prior written permission from Green Hills Software, Inc and Advanced Data Controls Corp.

Green Hills, the Green Hills logo, CodeBalance, GMART, GSTART, INTEGRITY, MULTI, and Slingshot are registered trademarks of Green Hills Software, Inc.

AdaMULTI, Built with INTEGRITY, EventAnalyzer, G-Cover, GHnet, GHnetLite, Green Hills Probe, Integrate, ISIM, u-velOSity, PathAnalyzer, Quick Start, ResourceAnalyzer, Safety Critical Products, SuperTrace Probe, TimeMachine, TotalDeveloper, DoubleCheck, and velOSity are trademarks of Green Hills Software, Inc.

All other company, product, or service names mentioned in this book may be trademarks or service marks of their respective owners.

| Chapter 1 | Introduction                                 | 1  |

|-----------|----------------------------------------------|----|

| Chapter 2 | Notational Conventions                       | 3  |

| Chapter 3 | Files                                        | 5  |

| Chapter 4 | Setup                                        | 7  |

|           | Setup with Windows                           | 8  |

|           | Connect to ICEs                              |    |

|           | The File Necessary at the Execution          | 8  |

|           | Setting of environment variable              | 9  |

| Chapter 5 | Starting 850eserv2 and debugging             | 11 |

|           | Connects via Connection Oganizer             | 12 |

|           | Connection Oganizer overview                 |    |

|           | Selects Connection method type               | 13 |

|           | Creates connection method                    | 13 |

|           | Connects via MULTI command pane              | 18 |

|           | connect command                              |    |

|           | Server Starting Options                      | 19 |

|           | Downloads user program                       | 27 |

|           | Start debugging                              | 29 |

|           | An error when connection and debugging       | 31 |

| Chapter 6 | Editing MULTI Resource Files                 | 35 |

|           | Overview                                     | 36 |

|           | Example of resource files                    |    |

|           | SERVERTIMEOUT                                |    |

|           | Starting 850eserv2                           |    |

|           | Target command                               | 38 |

|           | MULTI setup script                           | 39 |

|           | Note by MULTI resource file and setup script |    |

| Chapter 7 | I/O Pane                                     | 41 |

|           |                                              |    |

| Chapter 8  | Target Pane                         | 43 |

|------------|-------------------------------------|----|

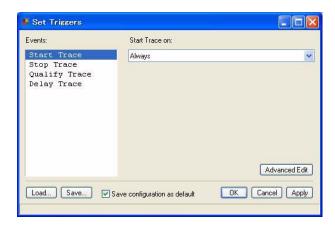

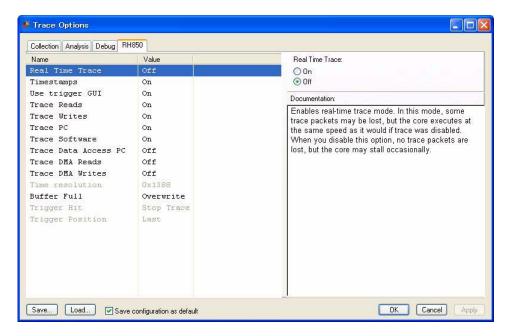

| Chapter 9  | Trace Analysing                     | 45 |

|            | Use SuperTrace Probe                | 46 |

|            | Setting of SuperTrace Probe         | 46 |

|            | Connects to SuperTrace Probe        | 46 |

|            | Use QB-V850E2-SP                    | 47 |

|            | Enable or Disable trace             | 48 |

|            | Launching TimeMachine               | 48 |

|            | Trace Trigger setting               |    |

|            | Trace Configurations                |    |

| Chapter 10 | O Hot-plugin debugging              | 53 |

|            | Launch 850eserv2 in Hot-plugin mode | 54 |

|            | Launch 850eserv2                    |    |

|            | Connect to Hot-plugin adapter       |    |

|            | Attach to target program            | 55 |

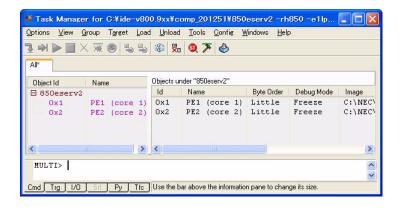

| Chapter 11 | 1 Multi-core debugging              | 57 |

|            | Multi-core debugging                | 58 |

|            | Launch 850eserv2                    |    |

|            | Target List                         | 58 |

|            | Load executable image to core       | 59 |

|            | Start debugging                     | 61 |

|            | Task Manager                        |    |

|            | Event setting                       | 62 |

| Chapter 12 | 2 Breakpoints                       | 63 |

|            | Software breakpoints                | 64 |

|            | Hardware breakpoints                |    |

|            | Breakpoints window                  |    |

| Chapter 13 | 3 The attestation code              | 67 |

| •          | About the attestation ID code       | 68 |

|            |                                     |    |

| Chapter 14 | 4 Target Commands                  | 69 |

|------------|------------------------------------|----|

|            | Command List Common to Server      | 70 |

|            | TARGET Commands Common to Servers  | 72 |

|            | ADDRESSOF                          | 72 |

|            | AMASK                              | 72 |

|            | BREAK                              | 73 |

|            | BLOCKFILL                          | 73 |

|            | CLOSE                              | 74 |

|            | DELBREAK                           | 74 |

|            | DELRANGE                           | 74 |

|            | DELRANGEALL                        | 75 |

|            | ECHO                               | 75 |

|            | FPRINT                             | 75 |

|            | FPRINTB                            |    |

|            | FREAD                              | 76 |

|            | FREADB                             | _  |

|            | GETENV                             |    |

|            | HALT                               |    |

|            | LISTRANGE                          |    |

|            | LISTVARS                           |    |

|            | LOAD                               |    |

|            | M                                  |    |

|            | MEMTEST                            | _  |

|            | NOFAIL                             |    |

|            | NOLOAD                             |    |

|            | OPEN                               |    |

|            | PRINT                              |    |

|            | RANDOM                             | _  |

|            | REG                                | _  |

|            | REGNUM                             |    |

|            |                                    |    |

|            | SCRIPT                             |    |

|            | SETRANGE                           |    |

|            | SETUPSLEEP                         |    |

|            | STATUS                             |    |

|            | STEP                               | •  |

|            | SYSCALLS                           | •  |

|            | UNDEF                              |    |

|            | Command List 850eserv2 Peculiar    |    |

|            | Target Commands 850eserv2 Peculiar |    |

|            | raruel Cummanus obueservz Pecunar  | 90 |

| PINMASK155                                   |

|----------------------------------------------|

| PIO158                                       |

| PIOBASE159                                   |

| PROFILE160                                   |

| RMEM161                                      |

| RRAMBASE163                                  |

| SFR164                                       |

| SHOWALL167                                   |

| SW168                                        |

| SYNCDEBUG169                                 |

| TCLEAR170                                    |

| TDISPLAY                                     |

| TFILTER                                      |

| TIMEBASE                                     |

| TIMER                                        |

| TMEVENT                                      |

| TMODE                                        |

| TRACE                                        |

| TRACEOFT                                     |

| TSIZE                                        |

| TSTOP                                        |

| TSEARCH                                      |

| TTIMER                                       |

| UNASSEMBLE200                                |

| VERIFY                                       |

| VERSION202                                   |

| WORKRAM205                                   |

| 850eserv2 Peculiar Command Available List206 |

| 850eserv2 Scripts209                         |

| Expressions210                               |

| Assignment211                                |

| Keyword211                                   |

| Conditions211                                |

| Loop212                                      |

| Extension of Variables212                    |

| Script Examples213                           |

|                                              |

| Chapter 15 Configuration Window217           |

|            | Starting Configuration Window                           | 219 |

|------------|---------------------------------------------------------|-----|

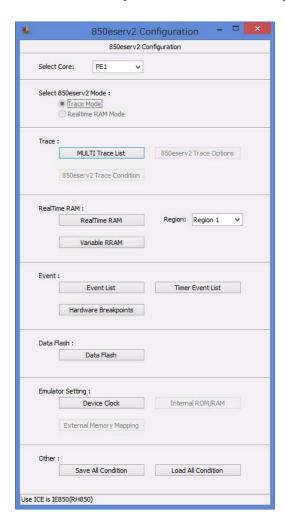

|            | Main window(850eserv2 Configuration)                    | 220 |

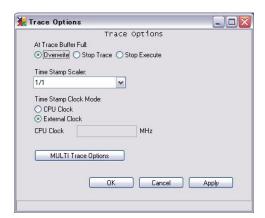

|            | Trace Options window                                    | 223 |

|            | Trace Condition window                                  | 224 |

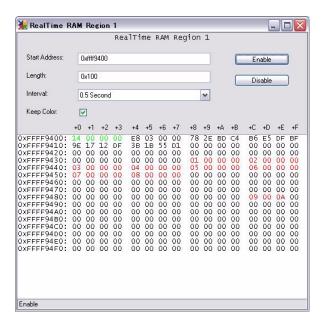

|            | Realtime RAM window                                     | 226 |

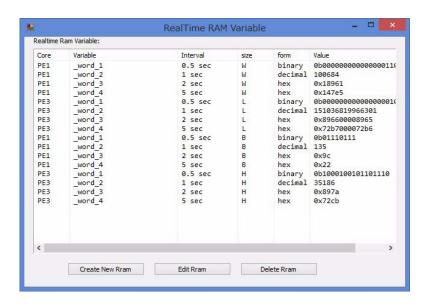

|            | Realtime RAM Variable window                            | 228 |

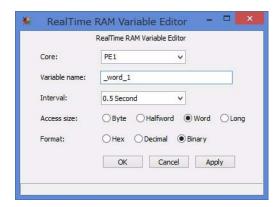

|            | Realtime RAM Variable editor                            | 229 |

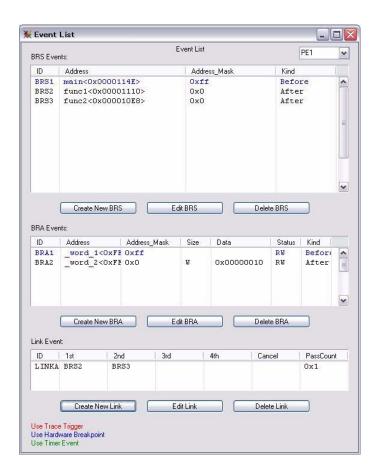

|            | Event List window                                       | 230 |

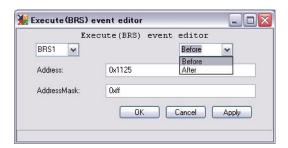

|            | Execute(BRS) event editor                               | 232 |

|            | Access(BRA) event editor                                | 233 |

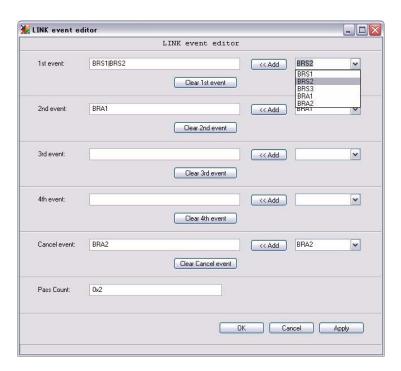

|            | LINK event editor                                       | 234 |

|            | Timer Event List window                                 | 236 |

|            | Timer Event Editor                                      | 238 |

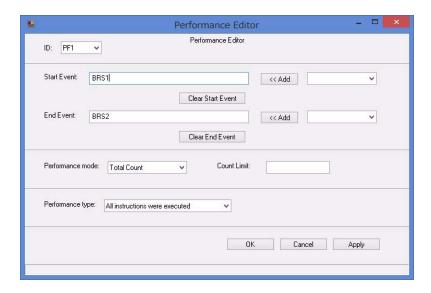

|            | Performance Editor                                      | 240 |

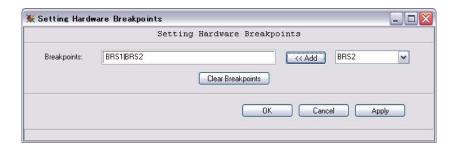

|            | Setting Hardware Breakpoints window                     |     |

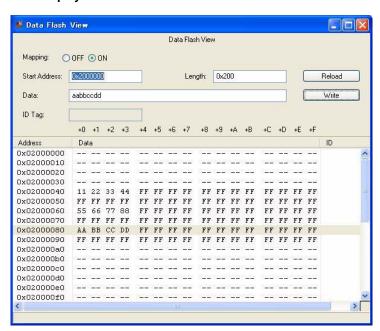

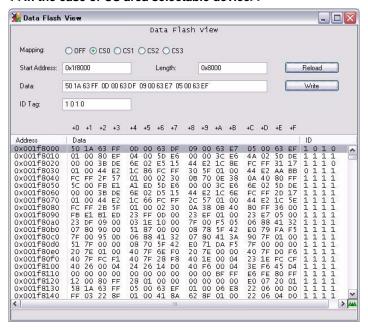

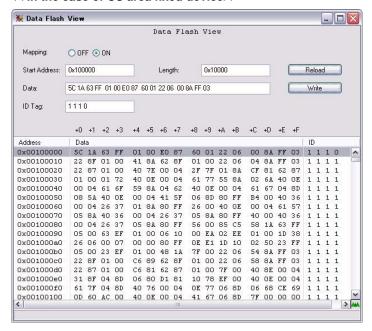

|            | Data Flash View                                         |     |

|            | Setting Device Clock window                             |     |

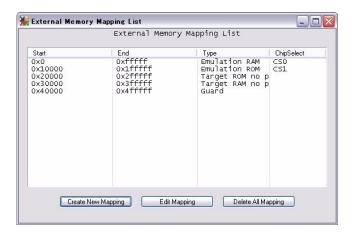

|            | External Memory Mapping List                            |     |

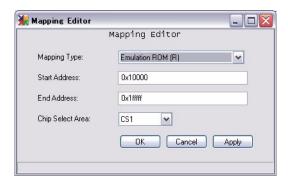

|            | External Memory Mapping Editor                          |     |

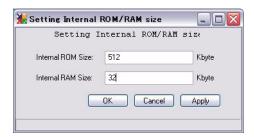

|            | Setting Internal ROM/RAM size window                    |     |

|            | ŭ                                                       |     |

| Chapter 16 | The changed part from 850eserv                          | 249 |

|            | Option List Which was Deleted from 850eserv             | 250 |

|            | Options Which was Deleted from 850eserv                 | 251 |

|            | -network                                                | 251 |

|            | -X0                                                     |     |

|            | -X1                                                     |     |

|            | -noint                                                  |     |

|            | Command List Which was Deleted or Changed from 850eserv |     |

|            | Commands Which was Deleted or Changed from 850eserv     |     |

|            | ASSEMBLEBATCH                                           |     |

|            | BREAK                                                   |     |

|            | CANCEL                                                  |     |

|            | CLOCK                                                   |     |

|            | COMBO                                                   | 255 |

|            | COMPARE                                                 | 256 |

|       | COPY                             | 256 |

|-------|----------------------------------|-----|

|       | DFVIEW                           | 256 |

|       | FILL                             | 257 |

|       | FIND                             | 257 |

|       | HISTORY                          | 257 |

|       | MEMORY                           | 258 |

|       | NOLOAD                           | 258 |

|       | PAUSE                            | 258 |

|       | PIO                              | 259 |

|       | PROFILE                          |     |

|       | REGISTER                         |     |

|       | RESET                            |     |

|       | RMEMVIEW                         |     |

|       | SFR                              |     |

|       | SYMBOL                           |     |

|       | TDISPLAY                         |     |

|       | TFILTER                          |     |

|       | TMODE                            |     |

|       | TRACEWIN                         |     |

|       | WAIT                             | 262 |

| Appen | dix AERROR Message From ICE      | 263 |

|       | Fatal Error                      | 264 |

|       | User system abnormality          | 268 |

|       | Status Error                     | 271 |

|       | Parameter Error                  | 275 |

|       | Device Dependent Error           | 277 |

|       | IECUBE or IE850 Starting Error   |     |

|       | IECUBE or IE850 Starting Warning |     |

|       | RSU verify Error                 |     |

|       | Server Starting Error            |     |

## **Chapter 1 Introduction**

This manual describes how to use MULTI with the V850/V850E ICE made by Renesas Electronics. The manual provides information on files included in the package and how to customize certain files. This manual is intended for users who already know about basic operations of MULTI. For detailed use of MULTI, please refer to MULTI related manuals.

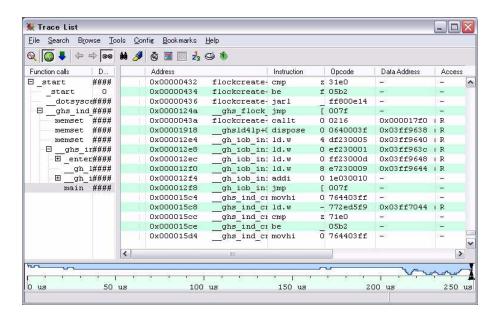

850eserv2 has succeeded the function of 850eserv almost and 850eserv2 supports TimeMachine which is the Advanced Capability of MULTI. You can use Trace produce in Trace List window and TimeMachine, with the combination of MULTI V4.0.7 or later,850eserv2 V2.000 or later, and IECUBE or IE850 made by Renesas Electronics.

You can use IE850+V850E2 Core with combination of MULTI V5.1.6 or later and 850eserv2 V2.005. You can use RH850 with E1 Emulator with combination of MULTI V6.1.4 or later and 850eserv2 V2.023.

You can use IE850+RH850 with combination of MULTI V6.1.4(V2013.1.5) or later and 850eserv2 V2.028.

You can use E2 Emulator+RH850 with combination of MULTI V6.1.6(V2015.1.7) or later and 850eserv2 V2.042.

Concerning the functional difference of 850eserv2 and 850eserv, please refer to "Chapter 16 The changed part from 850eserv" on page 249.

It is used in order to show the part where this kind of sign especially is important

#### Related document

Please refer to "E1/E2/E20 Emulator Additional Document for User's Manual" by Renesas Electronics.

## **Chapter 2 Notational Conventions**

Unless otherwise specified, the following conventions apply throughout the manual (They are subsets of "MULTI User's Guide"):

- \* Highlighted text (bold characters) contained in ordinary text indicates that it must be typed or output as specified.

- \* *Italicized characters* contained in ordinary or highlighted text indicates that they must be replaced with appropriate values.

- \* Commands or options enclosed in [ ] indicates that they are options.

- \*  $A \mid B \mid C$  indicates that one of A, B, and C should be typed as necessary.

- \* <cr> indicates the point where to press the Enter key.

This list provides information for making target connections using the emulators and interfaces listed in the table below.

| In-circuit emulator | Interface | Referred to in this book as   |

|---------------------|-----------|-------------------------------|

| IE-V850E1-CD-NW     | PCMCIA    | OCD Emulator(N-Wire Emulator) |

| MINICUBE            | USB       | OCD Emulator(MINICUBE)        |

| QB-MINI2            | USB       | MINICUBE2                     |

| E1 Emulator         | USB       | E1 Emulator                   |

| E20 Emulator        | USB       | E20 Emulator                  |

| E2 Emulator         | USB       | E2 Emulator                   |

| IECUBE              | USB       | IECUBE                        |

| IE850               | USB       | IE850                         |

## **Chapter 3 Files**

The V850/V850E ICE server (850eserv2) package includes the following files:

| file          | contents                                     |

|---------------|----------------------------------------------|

| 850eserv2.exe | V850/V850E ICE server by Renesas Electronics |

| 850win.exe    | 850eserv2 Configuration window application   |

| tipserv.exe   | TIP supporting application                   |

# Chapter 4 Setup

This chapter describes the following items.

o Setup with Windows

#### **Setup with Windows**

Insert the supplied disk into the appropriate drive of the PC then, from the Windows Program Manager, execute setup.exe on the diskette. This completes basic installation of the server.

#### **Connect to ICEs**

#### << In case of N-Wire Emulator>>

Before using 850eserv2, you must properly configure the PC, interface card, ICE, card-type ICE, and target system. Make sure that these have been properly set up. 850eserv2 uses the interface card to communicate with each ICE. Before operating 850eserv2, install the Renesas Electronics interface card device driver to enable the card. Refer to the interface card manual for details of the device driver.

#### << In case of MINICUBE, MINICUBE2, E1/E2/E20 emulator, IECUBE, IE850>>

Before using 850eserv2, you must properly configure the PC, USB driver and each ICE. Make sure that these have been properly set up. 850eserv2 uses the USB to communicate with the each ICE. Before operating 850eserv2, install the Renesas Electronics USB driver to enable the USB.

You can download USB driver for each ICE from following web page:

http://www.renesas.com/ghs debug if

For details of the each ICE and USB driver, please refer to the each ICE Setup Manual included with the each ICE.

#### The File Necessary at the Execution

The EXEC library, Device file and USB driver by Renesas Electronics are needed to debug in 850eserv2. You can download these tools from following web page:

http://www.renesas.com/ghs\_debug\_if

Uses EXEC library corresponding to each ICE.

| ICE                                                                           | EXEC library name |

|-------------------------------------------------------------------------------|-------------------|

| N-Wire Emulator, MINICUBE,<br>E1/E20 Emulator(JTAG), IECUBE                   | EX850G32.DLL      |

| MINICUBE2, E1/E20 Emulator(Serial)                                            | EX850O32.DLL      |

| MINICUBE+V850E2Core,<br>E1/E20 Emulator(JTAG)+V850E2Core,<br>IE850+V850E2Core | EX850G32E2R.DLL   |

| MINICUBE2+V850E2Core,<br>E1/E20 Emulator(Serial)+V850E2Core                   | EX850O32E2R.DLL   |

| E1/E20 Emulator(LPD)+V850E2Core                                               | EX850L32E2R.DLL   |

| ICE                                           | EXEC library name |

|-----------------------------------------------|-------------------|

| E1/E2/E20 Emulator(LPD)+RH850,<br>IE850+RH850 | EXRH850G3.DLL     |

All files in EXEC library package are needed. Please prepare all files in EXEC library package into MULTI compiler or 850eserv2 installed directory.

#### Setting of environment variable

There are two Windows environment variables that must be set: IEPATH and DEVICE\_FILE. The following sections describe each environment variable. Windows environment variables can be set from "Advanced" tag in System Properties window(righet-click on "My Computer" and choose "Properties").

#### The IEPATH Environment Variable

The IEPATH environment variable should be set to specify the directory where the Device file is located. For example, the Device file is located in *C*:\( |green\)\( v850e:\)

Variable name : IEPATH

Variable Value: C:\green\v850e

#### The DEVICE\_FILE Environment Variable

The DEVICE\_FILE environment variable should be set to specify the Device file name that contains the appropriate target-specific information. The specified device file must exist in the directory specified by IEPATH. For example, the Device file name is *DF3283.800* for V850ES/SG2:

Variable name : DEVICE\_FILE Variable Value: DF3283.800

## Chapter 5 Starting 850eserv2 and debugging

This chapter describes the following items.

- o Connects via Connection Oganizer

- o Connects via MULTI command pane

- o Downloads user program

- o Start debugging

- o An error when connection and debugging

You can start 850eserv2 via **connect** command in MULTI command pane or Connection Editor wondow in Connection Oganizer. It describes two method in this chapter.

### **Connects via Connection Oganizer**

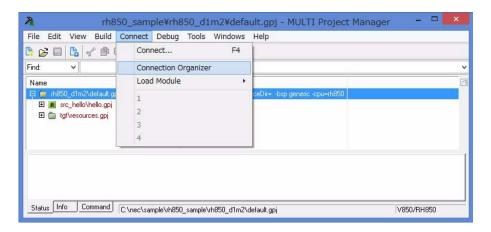

You can connect to 850eserv2 via Connection Oganizer. Connection Oganizer can be opened via "Connect > Connection Oganizer" in MULTI Project Manager or "Target > Show Connection Oganizer" in MULTI debugger menu.

#### **Connection Oganizer overview**

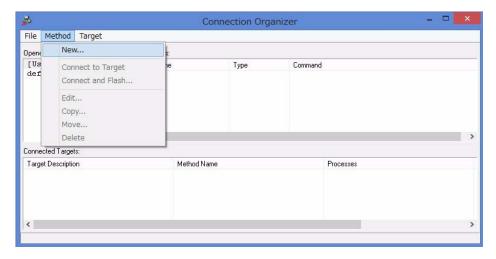

This window is opened when starts Connection Oganizer. The new connection method can be created via "Connection Editor" window which is opened via "Method > New" in menu. The created connection

method is dispayed in "User Method". You can connect to 850eserv2 when you click this method and select "Method > Connect to Target" in menu.

#### Selects Connection method type

This window is opened when you select "Method > New" in Connection Oganizer's menu. Please input arbitrary name to "Name:" and select "Renesas V850/850E ICE(850eserv2)" in "Type:". When you push "Create" button, Connection Editor window is opened.

#### Creates connection method

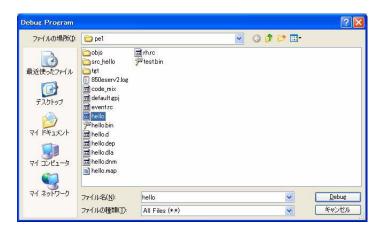

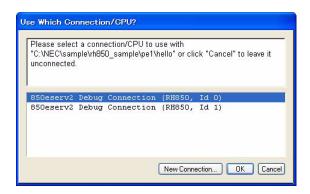

You can create a new connection method which is used to connect to 850eserv2 in this window. 850eserv2 is connected when push "Connect" button after set connection method. When it connects to 850eserv2 via MULTI Project Manager, MULTI debugger is opened automatically. In this case, please load executable image via "File > Debug Program" in MULTI debugger's menu.

Name: Inputs Connection method name.

Type: Shows Connection method type.

Log Connection

to file:

Output connection log between MULTI and 850eserv2 to speci-

fied file.

Target Setup

script:

Specifies setup script(.mbs file). This file is loaded automati-

cally when MULTI downloads target program.

Connect: Connects to 850eserv2.

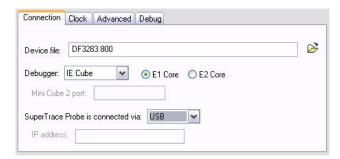

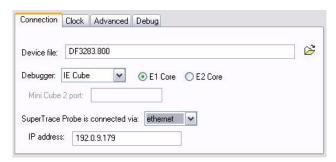

#### **Connection Tag**

Device File:

Specifies target Device file. If you do not specify an appropriate

Device file, you may be not able to debug correctly.

Debugger:

Selects use ICE.

When you connect V850E1 core or V850E2/ME3, you should select "E1 core". When you connect V850E2 core, you should select "E2 core". When you connect RH850, you should select "RH850".

If you select MINICUBE2 or E1/E20 Emulator(Serial), you should input a port name which is used to connect to MINICUBE2 into "Mini Cube 2 port:".

If you select E1/E2 Emulator, you should select supplied power from ICE to target(3v or 5v), or supplied from target(Target).

If you select E1/E2/E20 Emulator(LPD) and "RH850", you should select number of pins used LPD connection to "LPD pins:". When you select 1Pin, you should specify "Baudrate:" to 2000, 1000, 500(Kbps). When you select 4Pin, you should specify "LPD clock:" to 11000, 5500(KHz) or default. When you select default, it connects to ICE by default

LPD clock of device.

SuperTrace Probe is connected via:

Selects connection method with SuperTrace Probe. Default is no use with SuperTrace Probe(no STP). If you select "ethernet", you should input the IP address which is registered in SuperTrace

Probe into "IP address:".

#### **Clock Tag**

Device Clock Rate:

Specifies target operating frequencies(Device Clock). When not set target's operating frequencies, or when the wrong value is set,

Emulator cannot access to target device correctly.

For detail of each target operating frequencies, please refer to

each device manuals.

Main Clcok: Specifies Main clock per kHz.

When using the device supported internal clock, if input

"intclock", use internal clock.

Sub Clcok: Specifies Sub clock per Hz.

Use sub clock when break is hit?

If you select "Yes", emulator use Sub clock when program is

breaking.

When you select supplied power from ICE to target(3V or 5V), the target may not work correctly if selected supplied power unmatches the device specifications or the power voltage target requires. Please check it when select 3V or 5V.

#### **Advanced Tag**

Protect I/O memory:

Disables I/O memory protect. By default, you cannot view or change the I/O memory in MULTI and **SFR** command is needed

for this purpose.

Debug with RD850 or

AZ850:

Uses RD850 or AZ850 by Renesas Electronics.

Fast download to Flash memory:

Downloads all sections to Code flash memory at a time.

If this option is specified, 850eserv2 downloads all sections to Code flash memory at a time to reduce writing count to flash memory and become writing speed faster after progress bar is 100%, you cannot cancel downloading to Code flash memory.

Hot Plugin Debugging:

Launches Hot-plugin mode. For detail of Hot-plugin debugging, please refer "Chapter 10 Hot-plugin debugging" on page 53

**ICE name:** When it connects multiple ICE at same time, specify ICE name.

Specified ICE name is can be get from after the last "/" of Device instance path(In WindowsXP, Device instance ID) in USB driver. In V850E1 core or MINICUBE2, can not specify ICE name and

this setting is ignored.

Registry ID Code:

Specifies attestation ID code for unlock the RSU(ROM Security Unit). If your Device has RSU, you need to specify 20(V850E1 core), 24(V850E2 core) or 32(RH850) digits attestation ID code and unlock the RSU. For detail of RSU, please refer to "Chapter 13 The attestation code" on page 67.

Environment variable:

Specify the environment variables.

#### **RH850 Options Tag**

Set Jtag I/F when end debugging:

Sets connection interface to JTAG when debugging is finished. When debugger is finished unusually, connection interface can not be changed to JTAG.

It can be used with RH850.

Disable option byte settng

When this option is specified and the option-byte OPJTAG is different the setting by starting option, an error is returned and connecting is discontinued. If this option is not specified and OPJTAG is different, OPJTAG is changed and connecting is continued.

It can be used with RH850.

Disable to change clock when write to flash

Does not allow to change clock when writing or erasing to flash memory. For the detail of changeing clock, please refer to "FLASHCLOCK" on page 119.

It can be used with RH850.

Not initialize to RAM

Not initialize to RAM in startup. If it accesses to RAM before RAM initialization, the ECC error is detected.

It can be used with RH850.

Cold Starting

Does not do the setting which uses PiggyBack board in connecting PiggyBack board.

When using a micro-controller that need setting for PiggyBack board, 850eserv2 do the setting which uses PiggyBack board automatically in connecting PiggyBack board in default.

850eserv2 does not do this setting if this option is specified. When uses PiggyBack board with this option, 850eserv2 may not able to

It can be used with RH850.

connect to emulator.

Use software break-point:

Use software breakpoint by writing instruction.

It can be used with RH850.

In RH850, usually it uses hardware breakpoint at breakpoint. When turn on to **Use software breakpoint:**, it uses software breakpoint by writing instruction. For the detail of breakpoints, please refer to "Chapter 12 Breakpoints" on page 63.

#### **Debug Tag**

The items in this tag are using to debug into 850eserv2. Therefore, you do not need to specify these usually.

### **Connects via MULTI command pane**

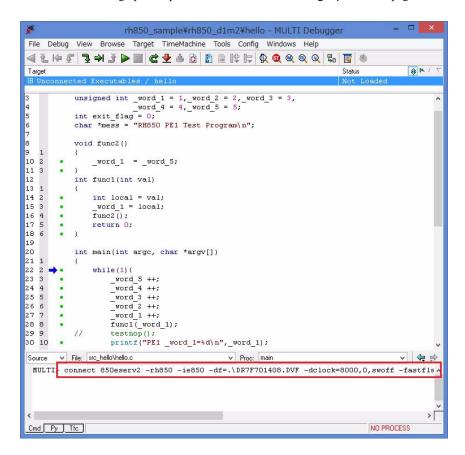

#### connect command

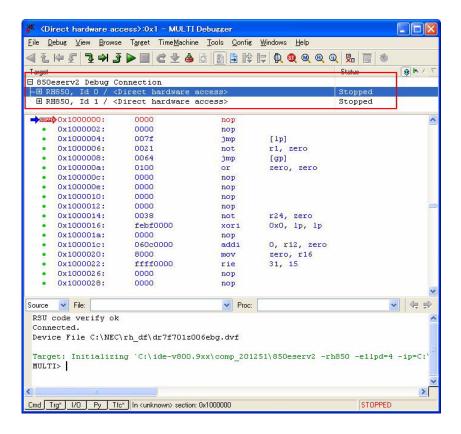

You can use **connect** command to connect to 850eserv2. **connect** command is input in MULTI debugger command pane(Red pane in following image) and can be attached each starting options. For the detail of these starting options, please refer to "Server Starting Options" on page 19.

Following is an exapmle of **connect** command:

```

connect 850eserv2 -iecube -df=DF3283.800

```

If the connection to 850eserv2 is successful, the following will appear on MULTI command pane:

```

Connected to target `850eserv2...'

```

If following message is displayed in MULTI command pane:

Please specify DEVICE FILE using DEVICE\_FILE environment variable

Please specify Device file name by environment variable DEVICE\_FILE or starting option -df. Or if following message is displayed in MULTI command pane:

```

Module 'ex850g32.dll' not found Unable to connect to emulator

```

Please confirm to prepare the EXEC library in MULTI or 850eserv2 installed directory. For the detail of other error message, please refer to "Appendix A ERROR Message From ICE" on page 263.

#### **Server Starting Options**

There are those below in starting option. Starting option distinguishes capital letter and the small letter. It attaches these options with **connect** command.

#### <<Only OCD emulator and E1/E20 emulator(JTAG) specifiable options>>

| -cdnw     | Connects through PCMCIA to N-Wire emulator(IE-V850E1-CD-NW).                                                                        |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------|

| -2m       | Sets the DCK to 10 MHz because of compatibility with 2-meter cables. Default DCK of N-Wire emulator is 20MHz.(Only N-Wire emulator) |

| -minicube | Connects through USB to MINICUBE.                                                                                                   |

| -e1jtag   | Connects through USB to E1 Emulator JTAG.                                                                                           |

| -e20jtag  | Connects through USB to E20 Emulator JTAG.                                                                                          |

| -dck20    | Sets the DCK to 20 MHz. Default DCK of MINICUBE is 10MHz. (Only MINICUBE or E1/E20 emulator(JTAG))                                  |

When -e1lpd or -e20lpd are specified, it needs the EXEC library for only LPD (Low Pin debug) (EX850L32E2R.DLL). When its connects to RH850, it needs the EXEC library for only RH850(EXRH850G3.DLL).

#### <Only MINICUBE2 and E1/E20 emulator(Serial) specifiable options>>

| -minicube2                | Connects through USB to MINICUBE2.                                                                                                                                                                               |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -e1serial                 | Connects through USB to E1 Emulator Serial.                                                                                                                                                                      |

| -e20serial                | Connects through USB to E20 Emulator Serial.                                                                                                                                                                     |

| -p= <port name=""></port> | Specify use port name to connect target. If device does not support specified port name, it can not connect to MINICUBE2. In that case, error message and the port name list that can be specified is displayed. |

| -writemon                 | Does not display error message when write to Monitor reserved area.                                                                                                                                              |

#### **Example:**

connect 850eserv2 -minicube2 -p=uarta0

#### <<Only E1/E2/E20 emulator(LPD) specifiable options>>

| -e1lpd                          | Connects through USB to E1 Emulator LPD in V850E2 Core.                                                                         |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                                 |                                                                                                                                 |

| -e20lpd                         | Connects through USB to E20 Emulator LPD in V850E2 Core.                                                                        |

| -e1lpd1= <baudrate></baudrate>  | Connects through USB to E1 Emulator LPD by 1pins mode in RH850. You should specify "baudrate" to 2000, 1000, 500(Kbps).         |

| -e1lpd4=< <i>LPD clock</i> >    | Connects through USB to E1 Emulator LPD by 4pins mode in RH850. You should specify "LPD clock" to 11000, 5500(KHz) or default.  |

| -e2lpd1= <baudrate></baudrate>  | Connects through USB to E2 Emulator LPD by 1pins mode in RH850. You should specify "baudrate" to 2000, 1000, 500(Kbps).         |

| -e2lpd4=< <i>LPD clock</i> >    | Connects through USB to E2 Emulator LPD by 4pins mode in RH850. You should specify "LPD clock" to 11000, 5500(KHz) or default.  |

| -e20lpd1= <baudrate></baudrate> | Connects through USB to E20 Emulator LPD by 1pins mode in RH850. You should specify "baudrate" to 2000, 1000, 500(Kbps).        |

| -e20lpd4=< <i>LPD clock</i> >   | Connects through USB to E20 Emulator LPD by 4pins mode in RH850. You should specify "LPD clock" to 11000, 5500(KHz) or default. |

| -dck20                          | Sets the DCK to 20 MHz. Default DCK of MINICUBE is 10MHz. (Only MINICUBE or E1/E20 emulator(JTAG))                              |

#### <<Only OCD emulator specifiable options>>

| -hotplugin | Launches Hot-plugin mode. For detail of Hot-plugin debugging, please refer "Chapter 10 Hot-plugin debugging" on page 53 |

|------------|-------------------------------------------------------------------------------------------------------------------------|

|------------|-------------------------------------------------------------------------------------------------------------------------|

#### <<Only E1/E2 emulator specifiable options>>

| -t3v | E1/E2 emulator supplies 3V power to target. |

|------|---------------------------------------------|

| -t5v | E1/E2 emulator supplies 5V power to target. |

When you select supplied power from ICE to target(use -t3v or -t5v), the target may not work correctly if selected supplied power unmatches the device specifications or the power voltage target requires. Please check it when use -t3v or -t5v.

#### <<Only IECUBE and IE850 specifiable options>>

| -iecube | Connects through USB to IECUBE.                                                                                                                                     |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -ie850  | Connects through USB to IE850.                                                                                                                                      |

| -tc     | Specifies that the target board be connected to IECUBE or IE850. If you specify this option, it detects unusual power status. Be sure to power on the target board. |

#### <<Only IECUBE specifiable options>>

| -stp <ip address="" hostname="" or=""></ip> | Specifies Green Hills SuperTrace Probe for LAN connection. IP address or hosname is required. |

|---------------------------------------------|-----------------------------------------------------------------------------------------------|

| -usb                                        | Specifies Green Hills SuperTrace Probe for USB connections.                                   |

#### <<Only V850E2Core specifiable options>>

| -nocache | This option is available for V850E2 Core.  Downloaded data into Code flash area is not cached.  The default behavior(without -nocache) is that downloaded data is cached. |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                                                                                                                                           |

#### <<Only RH850 specifiable options>>

| -opbyte_jtag    | This option is available for RH850. Sets connection interface to JTAG when debugging is finished. When debugger is finished unusually, connection interface can not be changed to JTAG.                                                                                                                  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -opbyte_disable | This option is available for RH850.  When this option is specified and the option-byte OPJTAG is different the setting by starting option, an error is returned and connecting is discontinued.  If this option is not specified and OPJTAG is different, OPJTAG is changed and connecting is continued. |

| -noflashclock   | This option is available for RH850.  Does not allow to change clock when writing or erasing to flash memory. For the detail of changing clock, please refer to "FLASHCLOCK" on page 119.                                                                                                                 |

| -noinitram               | This option is available for RH850.<br>Not initialize to RAM in startup. If it accesses to RAM before RAM initialization, the ECC error is detected.                                                                                                                                                                                                                                                                                                                |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -coldstart               | This option is available for RH850.  Does not do the setting which uses PiggyBack board in connecting PiggyBack board.  When using a micro-controller that need setting for PiggyBack board, 850eserv2 do the setting which uses PiggyBack board automatically in connecting PiggyBack board in default.  850eserv2 does not do this setting if this option is specified.When uses PiggyBack board with this option, 850eserv2 may not able to connect to emulator. |

| -cfapw <id code=""></id> | This option is available for RH850/P1x-C. Specifies attestation ID code for unlock to Code flash area by 64 digits code.                                                                                                                                                                                                                                                                                                                                            |

| -dfapw <id code=""></id> | This option is available for RH850/P1x-C. Specifies attestation ID code for unlock to Data flash area by 64 digits code.                                                                                                                                                                                                                                                                                                                                            |

| -useswbp                 | This option is available for RH850. Use software breakpoint by writing instruction.                                                                                                                                                                                                                                                                                                                                                                                 |

In RH850, usually it uses hardware breakpoint at breakpoint. When specifies -useswbp, it uses software breakpoint by writing instruction. For the detail of breakpoints, please refer to "Chapter 12 Breakpoints" on page 63.

#### << Each ICE common options >>

| -e1                   | Connects V850E1 core or V850E2/ME3                                                                                                                                                                                                                                                                                                                                          |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -e2                   | Connects V850E2 core. If "-e1", "-e2" or "-rh850" are omitted, 850eserv2 connects "-e1" core.                                                                                                                                                                                                                                                                               |

| -rh850                | Connects RH850.  If "-e1", "-e2" or "-rh850" are omitted, 850eserv2 connects "-e1" core.                                                                                                                                                                                                                                                                                    |

| -id <id code=""></id> | Specifies attestation ID code for unlock the RSU(ROM Security Unit). If your Device has RSU, you need to specify 20(V850E1 core), 24(V850E2 core), 32(RH850), or 64(RH850/P1x-C) digits attestation ID code and unlock the RSU. For detail of RSU, please refer to "Chapter 13 The attestation code" on page 67. If your Device does not have RSU, ID code becomes invalid. |

| -fastflashload                                                               | Downloads all sections to Code flash memory at a time. If this option is specified, 850eserv2 downloads all sections to Code flash memory at a time to reduce writing count to flash memory and become writing speed faster after progress bar is 100%, you cannot cancel downloading to Code flash memory. |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -noiop                                                                       | Disables I/O memory protect. By default, you cannot view or change the I/O memory in MULTI and <b>SFR</b> command is needed for this purpose. If this option is specified, you can view or change the I/O memory in MULTI.                                                                                  |

| -tip                                                                         | Uses RD850 or AZ850 by Renesas Electronics.                                                                                                                                                                                                                                                                 |

| -df = <df name=""></df>                                                      | Specify the device filename after "=". It is a usage similar to environment variable DEVICE_FILE. You can specify directory specification. In this case, you can omit "-ip".                                                                                                                                |

| -ip= <path></path>                                                           | Specify the directory where the device file is located after "=". It is a usage similar to environment variable IEPATH.                                                                                                                                                                                     |

| -dclock=<br><main_clock,<br>Sub_clock,<br/>swon   swoff&gt;</main_clock,<br> | Specifies target operating frequencies(Device Clock). The parameters which should be specified are same as <b>DCLOCK</b> command. Please refer to "DCLOCK" on page 101. When using the device supported internal clock, if input "intclock", use internal clock. In RH850, this option cannot be omitted.   |

| -ice <ice name=""></ice>                                                     | When it connects multiple ICE at same time, specify ICE name. Specified ICE name is can be get from after the last "/" of Device instance path(In WindowsXP, Device instance ID) in USB driver. In V850E1 core or MINICUBE2, can not specify ICE name and this setting is ignored.                          |

| -env <i><variable></variable></i>                                            | Specify the environment variables.                                                                                                                                                                                                                                                                          |

#### Example:

```

connect 850eserv2 -iecube -df=DF3288y.800 -ip=\green\v850e

-env V850_A=5,V850_B=args

```

When -df, -ip and environment variable DEVICE\_FILE, IEPATH are specified simultaneously, the device file and the directory specified by -df and -ip are given to priority.

#### << Each Server common options >>

As for options common to server, it can use even with the server of other companies make ICE correspondence other than 850eserv2.

| -nobss Variable section without an initial value section not to be downloaded. |

|--------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------|

| -nodata                   | Variable section with an initial value section not to be downloaded. |

|---------------------------|----------------------------------------------------------------------|

| -notext                   | Program code section not to be downloaded.                           |

| -noload                   | All section not to be downloaded.                                    |

| -bss                      | Variable section without an initial value section to be downloaded.  |

| -data                     | Variable section with an initial value section to be downloaded.     |

| -text                     | Program code section to be downloaded.                               |

| -loadall                  | All section to be downloaded.                                        |

| -nosyscalls               | It dosen't set a breakpoint in .syscall section when downloading.    |

| -setup< <i>filename</i> > | Script file which is specified is executed when downloading.         |

#### <<Starting options available list>>

| Option     | N-Wire<br>Emulator | MINI<br>CUBE | MIN<br>ICUBE2 | E1/E20<br>Emulator<br>(JTAG) | E1/E20<br>Emulator<br>(Serial) | E1/E2/E20<br>Emulator<br>(RH850) | IECUBE | IE850 | IE850<br>(RH850) |

|------------|--------------------|--------------|---------------|------------------------------|--------------------------------|----------------------------------|--------|-------|------------------|

| -cdnw      | Enable             | -            | -             | -                            | -                              | -                                | -      | -     | -                |

| -minicube  | -                  | Enable       | -             | -                            | -                              | -                                | -      | -     | -                |

| -minicube2 | -                  | -            | Enable        | -                            | -                              | -                                | -      | -     | -                |

| -eljtag    | -                  | -            | -             | Enable                       | -                              | -                                | -      | -     | -                |

| -e20jtag   | -                  | -            | -             | Enable                       | -                              | -                                | -      | -     | -                |

| -e1lpd     | -                  | -            | -             | Enable                       | -                              | -                                | -      | -     | -                |

| -e201pd    | -                  | -            | -             | Enable                       | -                              | -                                | -      | -     | -                |

| -ellpdl    | -                  | -            | -             | -                            | -                              | Enable                           | -      | -     | -                |

| -e1lpd4    | -                  | -            | -             | -                            | -                              | Enable                           | -      | -     | -                |

| -e2lpd1    | -                  | -            | -             | -                            | -                              | Enable                           | -      | -     | -                |

| -e2lpd4    | -                  | -            | -             | -                            | -                              | Enable                           | -      | -     | -                |

| -e201pd1   | -                  | -            | -             | -                            | -                              | Enable                           | -      | -     | -                |

| -e201pd4   | -                  | -            | -             | -                            | -                              | Enable                           | -      | -     | -                |

| Option          | N-Wire<br>Emulator | MINI<br>CUBE | MIN<br>ICUBE2 | E1/E20<br>Emulator<br>(JTAG) | E1/E20<br>Emulator<br>(Serial) | E1/E2/E20<br>Emulator<br>(RH850) | IECUBE | IE850  | IE850<br>(RH850) |

|-----------------|--------------------|--------------|---------------|------------------------------|--------------------------------|----------------------------------|--------|--------|------------------|

| -elserial       | -                  | -            | -             | -                            | Enable                         | -                                | -      | -      | -                |

| -e20serial      | -                  | -            | -             | -                            | Enable                         | -                                | -      | -      | -                |

| -iecube         | -                  | -            | -             | -                            | -                              | -                                | Enable | -      | -                |

| -ie850          | -                  | -            | -             | -                            | -                              | -                                | -      | Enable | Enable           |

| -e1             | Enable             | Enable       | Enable        | Enable                       | Enable                         | -                                | Enable | -      | -                |

| -e2             | -                  | Enable       | Enable        | Enable                       | Enable                         | -                                | -      | Enable | -                |

| -rh850          | -                  | -            | -             | -                            | -                              | Enable                           | -      | -      | Enable           |

| -2m             | Enable             | -            | -             | -                            | -                              | -                                | -      | -      | -                |

| -dck20          | -                  | Enable       | -             | Enable                       | -                              | Enable                           | -      | -      | -                |

| -nocache        | -                  | Enable       | -             | Enable                       | -                              | -                                | -      | Enable | -                |

| -opbyte_jtag    | -                  | -            | -             | -                            | -                              | Enable                           | -      | -      | Enable           |

| -opbyte_disable | -                  | -            | -             | -                            | -                              | Enable                           | -      | -      | Enable           |

| -noflashclock   | -                  | -            | -             | -                            | -                              | Enable                           | -      | -      | Enable           |

| -useswbp        | -                  | -            | -             | -                            | -                              | Enable                           | -      | -      | Enable           |

| -noinitram      | -                  | -            | -             | -                            | -                              | Enable                           | -      | -      | Enable           |

| -coldstart      | -                  | -            | -             | -                            | -                              | Enable                           | -      | -      |                  |

| -cfapw          |                    |              |               |                              |                                | Enable                           |        |        |                  |

| -dfapw          |                    |              |               |                              |                                | Enable                           |        |        |                  |

| -ice            | -                  | Enable       |               | Enable                       | Enable                         | Enable                           | -      | Enable | Enable           |

| -p              | -                  | -            | Enable        | -                            | Enable                         | -                                | -      | -      | -                |

| -writemon       | -                  | -            | Enable        | -                            | Enable                         | -                                | -      | -      | -                |

| -hotplugin      | -                  | Enable       | -             | Enable                       | -                              | Enable                           | -      | -      | -                |

| -t3v            | -                  | -            | -             | Enable<br>(E1 only)          | Enable<br>(E1 only)            | Enable<br>(E1/E2 only)           | -      | -      | -                |

| -t5v            | -                  | -            | -             | Enable<br>(E1 only)          | Enable<br>(E1 only)            | Enable<br>(E1/E2 only)           | -      | -      | -                |

| Option         | N-Wire<br>Emulator | MINI<br>CUBE | MIN<br>ICUBE2 | E1/E20<br>Emulator<br>(JTAG) | E1/E20<br>Emulator<br>(Serial) | E1/E2/E20<br>Emulator<br>(RH850) | IECUBE | IE850  | IE850<br>(RH850) |

|----------------|--------------------|--------------|---------------|------------------------------|--------------------------------|----------------------------------|--------|--------|------------------|

| -stp           | -                  | -            | -             | -                            | -                              | -                                | Enable | -      | -                |

| -usb           | -                  | -            | -             | -                            | -                              | -                                | Enable | -      | -                |

| -tc            | -                  | -            | -             | -                            | -                              | -                                | Enable | Enable | Enable           |

| -id            | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | -      | Enable | Enable           |

| -fastflashload | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | -      | Enable | Enable           |

| -noiop         | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | Enable | Enable | Enable           |

| -df            | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | Enable | Enable | Enable           |

| -ip            | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | Enable | Enable | Enable           |

| -env           | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | Enable | Enable | Enable           |

| -tip           | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | Enable | Enable | Enable           |

| -nobss         | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | Enable | Enable | Enable           |

| -nodata        | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | Enable | Enable | Enable           |

| -notext        | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | Enable | Enable | Enable           |

| -noload        | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | Enable | Enable | Enable           |

| -bss           | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | Enable | Enable | Enable           |

| -data          | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | Enable | Enable | Enable           |

| -text          | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | Enable | Enable | Enable           |

| -loadall       | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | Enable | Enable | Enable           |

| -nosyscalls    | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | Enable | Enable | Enable           |

| -setup         | Enable             | Enable       | Enable        | Enable                       | Enable                         | Enable                           | Enable | Enable | Enable           |

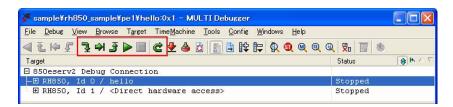

### Downloads user program

An executable image assigned to core is downloaded when push button in Debugger's toolber or load command via command pane in bottom of Debugger. If an executable image have not assigned to core in Multicore debugging, assign an execution imagevia "File > Debug Program" in Debugger menu.

If an executable image is downloaded to flash memory, use button or load command, not use "Fast Flash Programmer" in debugger. When the address of section in downloading image is in Flash memory area, 850eserv2 downloads this section to Flash memory automatically. The next message is shown when 850eserv2 is launched at first:

```

Please use 'load' for downloading to Flash memory, not use 'First Flash Programmer' in debugger.

This message is not shown in next connecting.

```

This message is not shown in next 850eserv2 launch.

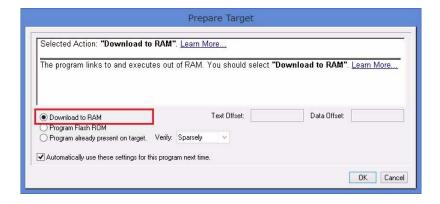

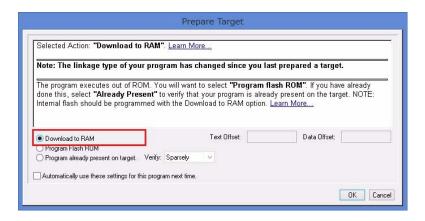

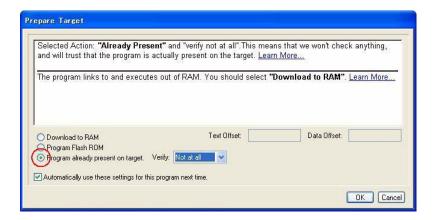

In first downloading, the next "Prepare Target" window may be opened. Select "Download to RAM" and push "OK" button in this window.

If you set that the target program runs from ROM(use standalone romrun.ld), the next is shown.

Please specify the target operating frequencies(Device Clock) by **DCLOCK** command before downloading. When not set target's operating frequencies, or when the wrong value is set, Emulator cannot access to target device correctly. In RH850, specify the target operating frequencies(Device Clock) via **Device Clock** Rate: in the Connection Editor window or -dclock option. If specified clock is different to the clock of oscillator on the target, The next error is displayed,

RSU info write error 0xca5: fatal err (could not connect to target)

Please check target connection and main clock specified with -dclock.

and 850eserv2 launching is failed.

If following message is displayed in MULTI command pane,

```

Download failed, error during write 0xnnnnnnnn - 0xmmmmmmmm debug server: download of "a.out" failed Load: Download failed.

```

downloading is failed for the each sections address in Linker directives file cannot be used on the device. Please check each sections address in Linker directives file. When next command is inputted to MULTI command pane after 850eserv2 launching:

### target cpu

memory map information of connectiong device is shown.

In case of V850E2Core, if you have not set the Flash Option area(Option-bytes) via **OPBYTE** command, following warning message is displayed.

```

WARNING: Flash Option area settings are default value. Use 'opbyte' command to change Flash Option area settings.

```

CPU is reset when you set the Flash Option area(Option-bytes) and attestation ID code for RSU.

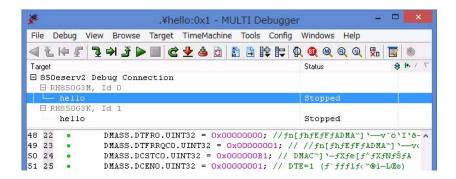

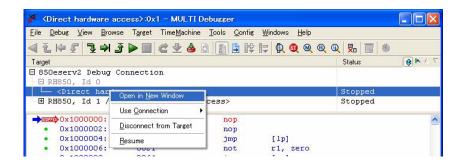

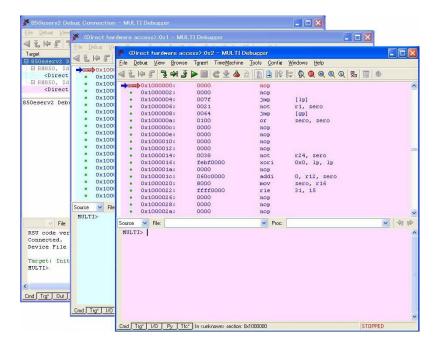

### Start debugging

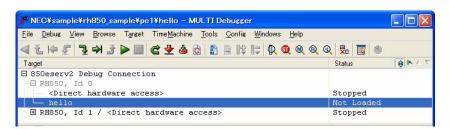

You can do Run-control to target via each icons in MULTI debugger tool bar after download an executable image to each cores in target. The Target List in top of debugger shows core's entry and core's status. In multi-core debugging, all cores' entry are shown. For the detail of multi-core debugging, please refer to "Chapter 11 Multi-core debugging" on page 57.

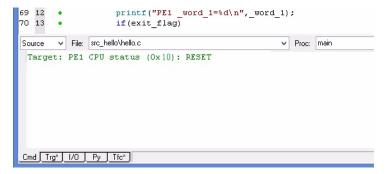

If core's status is changed in target is running, the next message is displayed in MULTI debugger command pane. In multi-core debugging, core name which changed status is displayed.

Displayed status is next.

| CPU status (0x1): WAIT           | CPU status is Waiting.               |

|----------------------------------|--------------------------------------|

| CPU status (0x2) : HOLD          | CPU status is Holding.               |

| CPU status (0x8) : HARDWARE STOP | CPU status is Stopping or Idle mode. |

| CPU status (0x10) : RESET        | CPU status is Reset.                 |

| CPU status (0x20) : HALT         | HALT mode.                           |

| CPU status (0x100) : FETCH-STOP  | CPU status is Fetch-stop.            |

| CPU status (0x1000) : COMBO | User interrupt is being processed at combo break. |

|-----------------------------|---------------------------------------------------|

|-----------------------------|---------------------------------------------------|

850eserv2 checks the core's status at a certain period while target running. Therefore, there is a case that it is different actually status changing timing and displayed message timing. You can check current core's status by **CPUSTATUS** command.

### An error when connection and debugging

It explains the error when connecting to 850eserv2 and debugging and how to resolve the error. The next are applied in RH850..

| Display 0xc70 error when connecting to 850eserv2 and connection is failed.                     | Specified Device file may be incorrect. Please use correct Device file matched your target device. If correct Device file is unknown, please contact to Renesas Electronics.                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Display "Code(Data) Flash security ID-code is not specified" message and connection is failed. | It is neccesaly to specify attestation ID-code for Code/<br>Data flash. Please specify 64 digits ID-code with <b>-cfapw</b><br>or <b>-dfapw</b> .                                                                                                                                                                                                                                                                                                                                                   |

| Display 0xca5 error when connecting to 850eserv2 and connection is failed.                     | When OPJTAG automatic setting is enabled for the setting of the debugger(It is enable in default), switch the device to the serial programming mode when it is connected and check and change the value of the OPJTAG bit in the option byte. If this fails, this error shown. Check the following items.                                                                                                                                                                                           |

|                                                                                                | * Device clock value specified by <b>-dclock</b> option may be incorrect. Please specify the frequency value of oscillator on your board. If oscillator prints 20MHz, you set next <b>-dclock</b> option.  -dclock=20000,0,swoff                                                                                                                                                                                                                                                                    |

|                                                                                                | * Control of pin resets for the transition to the serial programming mode may be wrong. When an emulator is connected, do not input a reset signal to the pin on the circuit other than from the emulator. Check the notes (e.g. the time the signal takes to reach the high level from the low level) given in "Connecting the RESET pin" in "E1/E20 Emulator Additional Document" by Renesas or whether the electrical characteristics requirements of the reset pin of the device are satisfied. |

|                                                                                                | * The connection between the emulator and the target device may be wrong. Check the circuit between the emulator and the target device.                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                | * Check that mode pins such as FLMD1, which are not controlled by the emulator, are being handled in ways that allow transitions to the serial programming mode.                                                                                                                                                                                                                                                                                                                                    |

Display 0xca8 error when connecting to Failed to LPD connection to target. 850eserv2 and connection is failed. Power may not be supplied to your target board correctly. If it supplies power from E1/E2 emulator to the board, power may not be supplied correctly by the target configuration. In the case, please supply power from external(use AC adapter) directly. When disable OPJTAG automatic setting (set "Disable option byte settng"), the OPJTAG bit in the option byte may not be specifying the correct connection interface (LPD). In this case, use Renesas Flash Programmer to change the value of the OPJTAG bit before connecting the debugger. When the emulator is connected other than with a hot plug-in connection, although the emulator controls the pin reset, this may fail. Check the notes (e.g. the time the signal takes to reach the high level from the low level) given in "Connecting the RESET pin" in "E1/E20 Emulator Additional Document" by Renesas or whether the electrical characteristics requirements of the reset pin of the device are satisfied. The connection between the emulator and the target device may be wrong. Check the circuit between the emulator and the target device. The specifications for communications may not be being satisfied due to the state of the target board. Set the LPD transfer rate to a low rate and check whether the emulator can then be re-connected. \* The condition on the time required for preparing communications before the emulator is connected to the target device may not be being satisfied. Use Renesas Flash Programmer to erase the code flash memory and check whether this makes the emulator connectable to the target device The target CPU may enter to standby mode(DEEPSTOP Display 0xc70 error when debugging and can not conrtol target. The target CPU wakes up when emulator handles, set OCD wake-up bit in WUFMSK0 register to 0 by SFR target command before debugging. OCD wake-up bit depends on the device.

| Inability to generate breaks                                                        | * The reset signal may have been at the active level for a long time. If a reset is input for more than 8 seconds, forced breaks will be disabled. Wait for the end of the reset input or change the setting for masking resets.                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                     | * Supply of a clock signal to the CPU may have stopped. Do not stop supply of a clock signal to the CPU. Cancel masking of resets and input a reset to the pin on the target board. When a breakpoint is set at the location indicated by the reset vector, debugging can be continued.                                                                                                                                                                                                   |

| Display 0x567 error when downloading or memory reading and memory access is failed. | Can not overlap memory access range to multiple memory regions(Code flash, Data flash, Local RAM, or Global RAM). You can check memory regions in the device by <b>CPU</b> target command.                                                                                                                                                                                                                                                                                                |

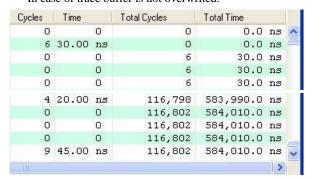

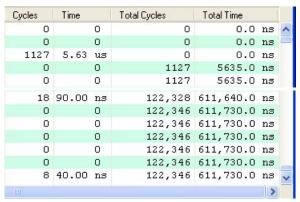

| SYSERR exception occurs during debugging.                                           | Debugger may access to Memory protection area.  When the target program is stopped in function, debugger reads memory from .stack area for get the information of call stack. If .stack area is Memory protection area, SYSERR exception occurs when next runs or steps. When debugger mode is "Memory Sensitive mode", debugger does not do this memory reading and SYSERR exception does not occur. You can change debugger mode to "Memory Sensitive mode" by next command. VOLATILE=1 |