# **MICROSAR OS RH850**

**Technical Reference**

| Authors | Senol Cendere, Yohan Humbert |  |  |

|---------|------------------------------|--|--|

| Version | 1.11                         |  |  |

| Status  | Released                     |  |  |

# **Document Information**

# History

| Author     | Date       | Version | Remarks                                              |

|------------|------------|---------|------------------------------------------------------|

| S. Cendere | 2014-01-21 | 1.00    | Creation                                             |

| S. Cendere | 2014-02-03 | 1.01    | Release for RH850 SafeContext                        |

| S. Cendere | 2014-04-24 | 1.02    | Release for RH850 P1M                                |

| S. Cendere | 2014-09-30 | 1.03    | Added error numbers for interrupt consistency checks |

| Y. Humbert | 2014-10-14 | 1.04    | Update                                               |

| Y. Humbert | 2015-01-29 | 1.05    | Added ASID support                                   |

| Y. Humbert | 2015-02-26 | 1.06    | Added D1M, E1L, E1M and F1M                          |

| Y. Humbert | 2015-06-10 | 1.07    | Added Multicore chapter                              |

| S. Cendere | 2015-06-29 | 1.08    | Added Timing Protection chapter                      |

| S. Cendere | 2015-08-20 | 1.09    | Removed core exception attributes                    |

| Y. Humbert | 2015-11-10 | 1.10    | Support Multicore SC3                                |

| S. Cendere | 2016-01-22 | 1.11    | Added description for osCheckAndRefreshTimer         |

# **Reference Documents**

| Ref. | Source                 | Title                                                                        | Version                 |

|------|------------------------|------------------------------------------------------------------------------|-------------------------|

| [1]  | AUTOSAR                | AUTOSAR Operating System Specification (downloadable from www.Autosar.org)   | 3.0.x<br>4.0.x<br>4.1.x |

| [2]  | OSEK                   | OSEK/VDX Operating System Specification (downloadable from www.osek-vdx.org) | 2.2.3                   |

| [3]  | Vector Informatik GmbH | Technical Reference MICROSAR OS                                              | 9.01                    |

# **Scope of the Document**

This technical reference describes the specific use of the MICROSAR OS for Renesas RH850. It supplements the general technical reference for MICROSAR OS [3].

#### Caution

We have configured the programs in accordance with your specifications in the questionnaire. Whereas the programs do support other configurations than the one specified in your questionnaire, Vector's release of the programs delivered to your company is expressly restricted to the configuration you have specified in the questionnaire.

#### Overview

This document describes the implementation specific part of the AUTOSAR operating system for the Renesas RH850 microcontroller family. In this document a processor of the family may be referred as RH850.

The common part of all MICROSAR OS implementations is described in document [3].

The implementation is based on the OSEK-OS-specification 2.2.3 and on AUTOSAR OS specifications 3.0.x/4.0.x/4.1.x. This document assumes that the reader is familiar with the OSEK and AUTOSAR OS specifications.

OSEK/VDX is a registered trademark of Continental Automotive GmbH (until 2007: Siemens AG).

# **Contents**

| 1 | Over                       | Overview of MICROSAR OS |                                               |    |  |  |

|---|----------------------------|-------------------------|-----------------------------------------------|----|--|--|

|   | 1.1                        | Overvie                 | ew of Properties                              | 8  |  |  |

| 2 | Insta                      | llation                 |                                               | 9  |  |  |

|   | 2.1                        | OIL-Co                  | onfigurator                                   | 9  |  |  |

|   |                            | 2.1.1                   | OIL-Implementation Files                      | 9  |  |  |

| 3 | Conf                       | iguration.              |                                               | 10 |  |  |

|   | 3.1                        | XML Co                  | onfiguration                                  | 10 |  |  |

|   | 3.2                        | OIL Co                  | nfiguration                                   | 10 |  |  |

|   | 3.3                        | OS Attr                 | ibutes                                        | 11 |  |  |

|   |                            | 3.3.1                   | MpuRegion Sub-Attributes (SC3 and SC4)        | 13 |  |  |

|   |                            | 3.3.2                   | PeripheralRegion Sub-Attributes (SC3 and SC4) | 14 |  |  |

|   | 3.4                        | Counte                  | r Attributes                                  | 15 |  |  |

|   |                            | 3.4.1                   | OSTM Sub-Attributes                           | 15 |  |  |

|   |                            | 3.4.2                   | OSTM_HIRES Sub-Attributes                     | 15 |  |  |

|   | 3.5                        | ISR Attı                | ributes                                       | 16 |  |  |

|   |                            | 3.5.1                   | ExceptionType Sub-Attributes                  | 16 |  |  |

|   | 3.6 Application Attributes |                         | 17                                            |    |  |  |

|   |                            | 3.6.1                   | Attribute MpuRegion                           | 17 |  |  |

|   | 3.7                        | Event A                 | Attributes                                    | 18 |  |  |

|   | 3.8                        | Linker I                | Include Files (SC3 and SC4)                   | 18 |  |  |

| 4 | Syste                      | em Genera               | ation                                         | 19 |  |  |

|   | 4.1                        | Code G                  | Generator                                     | 20 |  |  |

| 5 | Stack                      | ง Handling              | g                                             | 21 |  |  |

|   | 5.1                        | Task St                 | acks                                          | 21 |  |  |

|   | 5.2                        | ISR Sta                 | acks                                          | 21 |  |  |

|   | 5.3                        | System                  | n Stack                                       | 21 |  |  |

|   | 5.4                        | Startup                 | Stack                                         | 21 |  |  |

|   | 5.5                        | Stack U                 | Jsage Size                                    | 21 |  |  |

|   |                            | 5.5.1                   | Task Stack Usage                              | 22 |  |  |

|   |                            | 5.5.2                   | System Stack Usage                            | 22 |  |  |

|   |                            | 5.5.3                   | ISR Stack Usage                               | 22 |  |  |

| 6 | Inter                      | rupt Hand               | lling                                         | 23 |  |  |

|   | 6.1                        | Interrup                | ot Vectors                                    | 23 |  |  |

|   |                            | 6.1.1                   | Reset Vector                                  | 23 |  |  |

# Technical Reference MICROSAR OS RH850

|   |       | 6.1.2            | Level Init                                     | tialization                      | 23             |

|---|-------|------------------|------------------------------------------------|----------------------------------|----------------|

|   | 6.2   | Interrup         | t Level and                                    | Category                         | 24             |

|   | 6.3   | Interrup         | t Category                                     | 1                                | 24             |

|   |       | 6.3.1            | Interrupt                                      | Processing in C                  | 24             |

|   |       | 6.3.2            | Unhandle                                       | ed Exception Determination       | 24             |

|   | 6.4   | Interrup         | t Category 2                                   | 2                                | 25             |

|   |       | 6.4.1            | Interrupt                                      | Entry                            | 25             |

|   |       | 6.4.2            | Interrupt                                      | Exit                             | 25             |

|   |       | 6.4.3            | CAT2 ISF                                       | R Function                       | 25             |

|   | 6.5   | Disablin         | g Interrupts                                   | S                                | 25             |

| 7 | MPU   | Handling         | (SC3 and S                                     | SC4)                             | 26             |

|   | 7.1   | MPU Re           | egion Usage                                    | e                                | 26             |

|   |       | 7.1.1            | MPU Reg                                        | gion 0                           | 26             |

|   |       | 7.1.2            | Static MF                                      | PU Regions                       | 26             |

|   |       | 7.1.3            |                                                | MPU Regions                      |                |

| 8 | RH85  | 0 Periphe        | rals                                           |                                  | 28             |

|   | 8.1   | =                |                                                | Timer                            |                |

|   | 8.2   |                  | -                                              | onitoring Timer                  |                |

|   | 8.3   |                  |                                                |                                  |                |

| 9 | lmple | mentation        | n Specifics                                    |                                  | 29             |

| • | 9.1   |                  | -                                              |                                  |                |

|   |       | 9.1.1            |                                                | .IIInterrupts                    |                |

|   |       | 9.1.2            |                                                | IIInterrupts                     |                |

|   |       | 9.1.3            |                                                | AllInterrupts                    |                |

|   |       | 9.1.4            | •                                              | AllInterrupts                    |                |

|   |       | 9.1.5            |                                                | OSInterrupts                     |                |

|   |       | 9.1.6            | -                                              | OSInterrupts                     |                |

|   |       | 9.1.7            |                                                | urce                             |                |

|   |       | 9.1.8            |                                                | Resource                         |                |

|   |       | 9.1.9            |                                                | nBase                            |                |

|   |       | 9.1.10           |                                                | ze                               |                |

|   |       | 9.1.11           |                                                | ·C                               |                |

|   | 9.2   | Periphe          |                                                | API                              |                |

|   |       |                  |                                                |                                  |                |

|   |       | •                | 9.2.1.1                                        | Read Functions                   | 31             |

|   |       | ·                | •                                              | Read Functions                   |                |

|   |       | ·                | 9.2.1.1                                        | Write Functions                  | 32             |

|   | 9.3   | Periphe          | 9.2.1.1<br>9.2.1.2<br>9.2.1.3                  | Write Functions Modify Functions | 32             |

|   | 9.3   | Periphe<br>9.3.1 | 9.2.1.1<br>9.2.1.2<br>9.2.1.3<br>ral Interrupt | Write Functions                  | 32<br>33<br>34 |

|    |                                     | 9.3.2     | Set or Clear Mask Flag                        | 37 |  |  |

|----|-------------------------------------|-----------|-----------------------------------------------|----|--|--|

|    |                                     | 9.3.3     | Set or Clear ICR Request Flag                 | 38 |  |  |

|    |                                     | 9.3.4     | Read, Set or Clear Mask Bit in Registers IMRm | 39 |  |  |

|    |                                     | 9.3.5     | Write to Registers IMRm                       | 40 |  |  |

|    | 9.4                                 | Hook R    | Routines                                      | 41 |  |  |

|    |                                     | 9.4.1     | ErrorHook                                     | 41 |  |  |

|    |                                     | 9.4.2     | StartupHook                                   | 41 |  |  |

|    |                                     | 9.4.3     | ShutdownHook                                  | 41 |  |  |

|    |                                     | 9.4.4     | PreTaskHook                                   | 41 |  |  |

|    |                                     | 9.4.5     | PostTaskHook                                  | 41 |  |  |

|    |                                     | 9.4.6     | PreAlarmHook (SC1 only)                       | 41 |  |  |

|    |                                     | 9.4.7     | ISRHooks (SC1 only)                           | 42 |  |  |

|    |                                     | 9.4.8     | Callbacks (SC1 only)                          | 42 |  |  |

|    |                                     | 9.4.9     | ProtectionHook (SC3 and SC4)                  | 42 |  |  |

|    | 9.5                                 | Functio   | ns for MPU functionality checks               | 43 |  |  |

|    |                                     | 9.5.1     | Function osCheckMPUAccess                     | 43 |  |  |

|    |                                     | 9.5.2     | Function osCheckAndRefreshMPU                 | 44 |  |  |

|    | 9.6                                 | Functio   | on for OSTM functionality checks              | 45 |  |  |

|    |                                     | 9.6.1     | Function osCheckAndRefreshTimer               | 45 |  |  |

| 10 | Non-Trusted Functions (SC3 and SC4) |           |                                               |    |  |  |

|    | 10.1                                | Functio   | nality                                        | 46 |  |  |

|    | 10.2                                | API       |                                               | 47 |  |  |

|    | 10.3                                | Call Co   | ntext                                         | 48 |  |  |

|    |                                     | 10.3.1    | Example                                       | 49 |  |  |

| 11 | Multic                              | ore       |                                               | 50 |  |  |

|    | 11.1                                | Configu   | uration                                       | 50 |  |  |

|    |                                     | 11.1.1    | Core IDs                                      | 50 |  |  |

|    | 11.2                                | Multi-Co  | ore start-up                                  | 50 |  |  |

|    |                                     | 11.2.1    | Both PEs controlled by OS                     | 51 |  |  |

|    |                                     | 11.2.2    | Only PE1 controlled by OS                     | 51 |  |  |

|    |                                     | 11.2.3    | Only PE2 controlled by OS                     | 52 |  |  |

| 12 | Timin                               | g Protect | tion (SC4)                                    | 53 |  |  |

|    | 12.1                                | Configu   | uration Attributes                            | 53 |  |  |

|    | 12.2                                | Restrict  | tions for SC4 Configurations                  | 53 |  |  |

| 13 | Error                               | Handling  | ]                                             | 54 |  |  |

|    | 13.1                                | MICRO     | SAR OS RH850 Error Numbers                    | 54 |  |  |

|    |                                     | 13.1.1    | RH850 specific Error Numbers                  | 54 |  |  |

# Technical Reference MICROSAR OS RH850

| 14 Modules |       |              |  |    |

|------------|-------|--------------|--|----|

|            | 14.1  | Source Files |  | 56 |

|            | 14.2  | Header Files |  | 57 |

| 15         | Conta | nt .         |  | 59 |

# 1 Overview of MICROSAR OS

# 1.1 Overview of Properties

| Property Class                                    | Version / Range / Support                                                                                    |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| AUTOSAR OS specification                          | 3.0.x, 4.0.x, 4.1.x                                                                                          |

| Scalability Classes supported                     | SC1 SC3 (SafeContext) SC4 (SafeContext)                                                                      |

| Conformance Classes supported                     | SC1: BCC1, BCC2, ECC1, ECC2<br>SC3 and SC4: ECC2                                                             |

| Scheduling policy                                 | SC1: full-, non- and mixed-preemptive SC3 and SC4: full- and mixed-preemptive                                |

| Scheduling points                                 | depending on scheduling policy                                                                               |

| Maximum number of tasks                           | 65535                                                                                                        |

| Maximum number of events per task                 | 32                                                                                                           |

| Maximum number of activations per task            | 255                                                                                                          |

| Maximum number of priorities                      | 8192                                                                                                         |

| Maximum number of counters                        | 256                                                                                                          |

| Maximum number of alarms                          | 32767                                                                                                        |

| Maximum number of resources                       | 8192                                                                                                         |

| Maximum number of resources locked simultaneously | 255                                                                                                          |

| Maximum number of schedule tables                 | 65535                                                                                                        |

| Maximum number of expiry points                   | 65535 (cyclical expiry points counted by their multiplicity)                                                 |

| Maximum number of ISRs                            | depending on derivative                                                                                      |

| Status Levels                                     | SC1: STANDARD and EXTENDED SC3: EXTENDED SC4: EXTENDED                                                       |

| Nested Interrupts                                 | supported                                                                                                    |

| Interrupt level resource handling                 | SC1: supported SC3: not supported SC4: not supported                                                         |

| ORTI support                                      | SC1: 2.1 Standard and 2.1 Additional 2.2 Standard and 2.2 Additional SC3: 2.2 Additional SC4: 2.2 Additional |

| Library Version                                   | not supported                                                                                                |

| FPU support                                       | supported (if provided by derivative)                                                                        |

Table 1 OS Properties

# 2 Installation

The general installation is described in the common document [3].

The RH850 specific files are described below.

# 2.1 OIL-Configurator

The OIL-configurator is a general tool for different AUTOSAR implementations. The implementation specific parts are the code generator and the OIL-implementation files for the code generator.

OIL-Configurator root\OILTOOL

OIL-Implementation files root\OILTOOL\GEN

Code Generator root\OILTOOL\GEN

# 2.1.1 OIL-Implementation Files

The implementation specific files will be copied onto the local hard disk. The OIL-tool has knowledge about these files through the file OILGEN.INI (the correct path is set by the installation program).

| CPU      | Implementation file | Standard object file | Description         |

|----------|---------------------|----------------------|---------------------|

| D1L      | RH850_D1L.i41       | RH850_D1L.s41        | Source code version |

| D1M      | RH850_D1M.i41       | RH850_D1M.s41        | Source code version |

| E1L      | RH850_E1L.i41       | RH850_E1L.s41        | Source code version |

| E1M      | RH850_E1M.i41       | RH850_E1M.s41        | Source code version |

| E1x-FCC2 | RH850_E1x_FCC2.i41  | RH850_E1x_FCC2.s41   | Source code version |

| F1H      | RH850_F1H.i41       | RH850_F1H.s41        | Source code version |

| F1L      | RH850_F1L.i41       | RH850_F1L.s41        | Source code version |

| F1M      | RH850_F1M.i41       | RH850_F1M.s41        | Source code version |

| P1M      | RH850_P1M.i41       | RH850_P1M.s41        | Source code version |

Table 2 OIL implementation Files

# 3 Configuration

Before an application can be compiled all static MICROSAR OS objects have to be defined in a configuration file. The OS generator generates code in accordance to this configuration file.

The configuration can be done either in XML language (AUTOSAR ECU configuration format) or in OIL (OSEK implementation language).

Chapter 4 shows the program flow of a configuration / generation / compilation process in detail.

There are configuration attributes which are standard for all MICROSAR OS implementations. These are described in [3].

Platform specific attributes (which only apply to this implementation of MICROSAR OS) are described hereafter.

### 3.1 XML Configuration

An XML configuration of the OS must conform to the AUTOSAR XML schema. To edit such a configuration the DaVinci configurator of Vector Informatik GmbH can be used.

# 3.2 OIL Configuration

MICROSAR OS systems for RH850 can also be described using OIL. The OIL configurator tool is capable of reading and writing OIL files. The finished OIL file is passed to the code generator which generates the configuration files of the OS.

# 3.3 OS Attributes

The OS object controls general aspects of the operating system. The following attributes are provided for scalability class SC1, SC3 and SC4:

| Attribute Name              |                                 | Values                           | Description                                                                                                                                                                                |  |

|-----------------------------|---------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OIL                         | XML                             | Default value is written in bold |                                                                                                                                                                                            |  |

| Compiler                    | OsOSCompiler                    | GHS                              | Selects the supported compiler.                                                                                                                                                            |  |

| SystemStackSize             | OsOSSystemStackSize             | 0 0xFFFC                         | Size of the system stack in bytes.                                                                                                                                                         |  |

| EnumeratedUnhandl edISRs    | OsOSEnumeratedUnhandl edISRs    | TRUE<br>FALSE                    | This attribute determines handling of unused interrupt sources.  If set TRUE then variable ossUnhandledExceptionDetail is set to the exception number before calling osUnhandledException. |  |

| ORTIDebugSupport            | OsOSORTIDebugSupport            | TRUE<br>FALSE                    | The RH850 implementation supports ORTI debug information if this attribute is selected.                                                                                                    |  |

| ORTIDebugLevel              | OsOSORTIDebugLevel              | ORTI_22_Ad ditional              | Support ORTI 2.2 with additional features which require some additional runtime and memory.                                                                                                |  |

| UserConfigurationVe rsion   | OsOSUserConfigurationVer sion   | 0 0xFFFF                         | This value specifies the current user specific version of the OS configuration. It can be read back by the user for validation.                                                            |  |

| SupportFPU                  | OsOSSupportFPU                  | TRUE<br>FALSE                    | Switches on the support for FPU. (if provided by derivative)                                                                                                                               |  |

| TimingProtectionTim erClock | OsOSTimingProtectionTime rClock | 0 999999<br><b>No default</b>    | Only SC4: peripheral clock of timer unit TAUJ0 specified in [kHz]                                                                                                                          |  |

Table 1: RH850 specific attributes of OS

12 / 58

# For scalability class SC3 and SC4 the following additional attributes are provided:

| Attribute Name    |                       | Values                           | Description                                                                                                                                                                                               |

|-------------------|-----------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OIL               | XML                   | Default value is written in bold |                                                                                                                                                                                                           |

| CheckIntAPIStatus | OsOSCheckIntAPIStatus | TRUE<br>FALSE                    | If set to FALSE then the OS API functions CallTrustedFunction and CallNonTrustedFunction do not check the interrupt status.                                                                               |

| PeripheralRegion  | OsOSPeripheralRegion  | No default                       | List of peripheral regions. A peripheral region defines an address range where access is allowed for selected applications (trusted or non-trusted). The access is granted by means of the API functions. |

| MemoryProtection  | OsOSMemoryProtection  | TRUE<br>FALSE                    | Enables memory protection via MPU. Mandatory for SC3 and SC4.                                                                                                                                             |

| MpuRegion         | OsOSMpuRegion         | Enable                           | Configures static MPU regions                                                                                                                                                                             |

# 3.3.1 MpuRegion Sub-Attributes (SC3 and SC4)

If a static MPU region is enabled then the memory area is specified by the following subattributes:

| Sub-Attribute | Sub-Attribute Name |                                    | Description                                                                                                                                              |

|---------------|--------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| OIL           | XML                | (default value is written in bold) |                                                                                                                                                          |

| StartAddr     | OsOSStartAddr      | string<br>No default               | Start address of static MPU region hexadecimal value: StartAddr = 0x or memory area specific linker symbol: StartAddr = <li>linker_start_symbol&gt;</li> |

| EndAddr       | OsOSEndAddr        | string<br>No default               | End address of static MPU region hexadecimal value: EndAddr = 0x or memory area specific linker symbol: EndAddr = <li>linker_end_symbol&gt;</li>         |

| AccessRights  | OsOSAccessRights   | uint32<br>No default               | MPU region access configuration                                                                                                                          |

| ASID          | OsOSASID           | TRUE<br>FALSE                      | Specifies, whether ASID matching is enabled for this MPU region.                                                                                         |

| Identifier    | OsOSIdentifier     | 0 0x3FE<br><b>0x3FF</b>            | ASID value to be used as area match condition. The maximum value 0x3FF is used as default value.                                                         |

| CORE          | OsOSCORE           | uint32<br>No default               | Only Multicore OS: Core assignment for corresponding MPU region                                                                                          |

Value of StartAddr must always point to the first valid Byte in the specified memory area.

Value of EndAddr must always point to the last valid Byte in the specified memory area.

Version: 1.11

The number of configurable static MPU regions depends on the derivative.

```

MpuRegion = Enable

{

StartAddr = 0x...;

EndAddr = 0x...;

AccessRights = 0x...;

ASID = TRUE;

Identifier = 0x01;

CORE = 0;

};

/* Multicore OS */

};

```

# 3.3.2 PeripheralRegion Sub-Attributes (SC3 and SC4)

| Sub-Attribute Name        |                              | Values                                   | Description                                                                                                                                                                                                                    |

|---------------------------|------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OIL                       | XML                          | (default value<br>is written in<br>bold) |                                                                                                                                                                                                                                |

| StartAddress              | OsOSStartAddress             | uint32<br>No default                     | Numeric value.  Specifies the start address of the peripheral region which shall be configured.  Any 32 bit value can be used.                                                                                                 |

| EndAddress                | OsOSEndAddress               | uint32<br>No default                     | Numeric value.  Specifies the end address of the peripheral region which shall be configured.  Any 32 bit value can be used.                                                                                                   |

| Identifier                | OsOSIdentifier               | string<br>No default                     | C-String  Must be a unique C Identifier which can be used in an application or BSW module to access the peripheral region.                                                                                                     |

| ACCESSING_<br>APPLICATION | OsOSAccessing<br>Application | Application<br>Type                      | Application reference.  Defines access rights of an application for this PeripheralRegion.  This attribute can be defined multiple times, so that different applications might have access right to the same PeripheralRegion. |

# Caution

The application is allowed to access memory addresses in the interval of StartAddress <= memory to be accessed <= EndAddress

The "EndAddress" value is included! All bytes of a peripheral access must fit into the peripheral region.

©2016, Vector Informatik GmbH Version: 1.11 14 / 58

#### 3.4 Counter Attributes

Platform specific attributes are located within the container "DRIVER".

| Sub-Attribute Name |                | Values                             | Description                                                                                                                                                                                                                                                                              |

|--------------------|----------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OIL                | XML            | (default value is written in bold) |                                                                                                                                                                                                                                                                                          |

| Timer              | OsCounterTimer | OSTM<br>OSTM_HIRES<br>No default   | Selects the timer hardware which drives the hardware counter.  OSTM: OSTM timer is used and generates cyclic interrupts.  OSTM_HIRES: OSTM timer is used and runs in high resolution timer mode.  Which interrupt channel is used for a specific derivative can be found in chapter 8.1. |

# 3.4.1 OSTM Sub-Attributes

| Sub-Attribute Name |                             | Values                             | Description                                                                                                               |

|--------------------|-----------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| OIL                | XML                         | (default value is written in bold) |                                                                                                                           |

| EnableNesting      | OsCounterEnabl eNesting     | TRUE<br>FALSE<br>No default        | Specifies whether the timer interrupt which drives the hardware counter can be interrupted by higher priority interrupts. |

| InterruptPriority  | OsCounterInterr uptPriority | 0 <b>15</b><br>0 <b>7</b> (F1L)    | The priority of the timer ISR which drives the hardware counter.                                                          |

| StackSize          | OsCounterStack<br>Size      | 0 0xFFFC                           | Stack size of the timer ISR which drives the hardware counter.                                                            |

# 3.4.2 OSTM\_HIRES Sub-Attributes

| Sub-Attribute Name          |                                          | Values                             | Description                                                                                                                                  |  |

|-----------------------------|------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| OIL                         | XML                                      | (default value is written in bold) |                                                                                                                                              |  |

| EnableNesting               | OsCounterEnabl eNesting                  | TRUE<br>FALSE<br>No default        | Specifies whether the timer interrupt which drives the hardware counter can be interrupted by higher priority interrupts.                    |  |

| InterruptPriority           | OsCounterInterr uptPriority              | 0 <b>15</b><br>0 <b>7</b> (F1L)    | The priority of the timer ISR which drives the hardware counter.                                                                             |  |

| StackSize                   | OsCounterStack<br>Size                   | 0 0xFFFC                           | Stack size of the timer ISR which drives the hardware counter.                                                                               |  |

| MinTimeBetween<br>TimerIrqs | OsCounterMinTi<br>meBetweenTim<br>erIrqs | uint32<br><b>0</b>                 | Defines the number of timer ticks which at least must be between two timer interrupts (shortest possible time between two timer interrupts). |  |

Detailed description how to configure software and hardware counter can be found in [3].

©2016, Vector Informatik GmbH Version: 1.11 15 / 58

# 3.5 ISR Attributes

| Attribute Name          |                             | Values                           | Description                                                                                                                                                     |

|-------------------------|-----------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OIL                     | XML                         | Default value is written in bold |                                                                                                                                                                 |

| ExceptionType           | OsOSExceptionType           | GENERAL_EXCEPTION EIINT          | Select EIINT for EI level interrupts. Select GENERAL_EXCEPTION for core exceptions.                                                                             |

| EnableNesting           | OsOSEnableNesting           | TRUE<br>FALSE                    | Must be set FALSE if the configured CAT2 ISR shall not be interrupted by CAT1 or CAT2 ISRs with higher priority level. This attribute is ignored for CAT1 ISRs. |

| UseSpecialFunc tionName | OsOSUseSpecialFun ctionName | TRUE<br>FALSE                    | This is a feature for mapping different interrupt / exception sources to one interrupt handler. This feature is supported as described in [3].                  |

Table 2: RH850 specific ISR attributes

# 3.5.1 ExceptionType Sub-Attributes

# ExceptionType = GENERAL\_EXCEPTION

| Attribute Name   |                      | Values     | Description                      |

|------------------|----------------------|------------|----------------------------------|

| OIL              | OIL XML              |            |                                  |

| ExceptionAddress | OsOSExceptionAddress | No default | Interrupt vector address offset. |

Table 3: Sub-attributes of ExceptionType=GENERAL\_EXCEPTION

# ExceptionType = EIINT

| Attribute Name     |                        | Values                                     | Description                                                                              |

|--------------------|------------------------|--------------------------------------------|------------------------------------------------------------------------------------------|

| OIL                | XML                    |                                            |                                                                                          |

| IntChannel         | OsOSIntChannel         | 0 511<br>No default                        | Channel index of El level interrupt.  Max channel number depends on used CPU derivative. |

| InterruptPriority  | OsOSInterruptPriority  | SC1 and SC3: 015<br>SC4: 115<br>No default | Defines the interrupt priority level of the ISR. Lower value means higher priority.      |

| InterruptStackSize | OsOSInterruptStackSize | 0 0xFFFC<br>No default                     | Size of the ISR stack                                                                    |

Table 4: Sub-attributes of ExceptionType=EIINT

©2016, Vector Informatik GmbH Version: 1.11 16 / 58

# 3.6 Application Attributes

The following specific attributes are provided for SC3 and SC4:

| Attribute Name |                        | Values                           | Description                                                                                                   |

|----------------|------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------|

| OIL            | XML                    | Default value is written in bold |                                                                                                               |

| ASID           | OsApplicationASID      | 0 0x3FE<br>0x3FF                 | Value to be written to ASID register on application switch. The maximum value 0x3FF is used as default value. |

| MpuRegion      | OsApplicationMpuRegion | Enable                           | Configures application specific dynamic MPU region                                                            |

Table 5: RH850: Application specific attributes

# 3.6.1 Attribute MpuRegion

Attribute MpuRegion must be configured for non-trusted applications which need write access to application specific memory areas. If dynamic MPU region is enabled then the memory area is specified by following sub-attributes:

| Sub-Attribute Name |                            | Values                                   | Description                                                                                                                                                                                 |

|--------------------|----------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OIL                | XML                        | (default value<br>is written in<br>bold) |                                                                                                                                                                                             |

| StartAddr          | OsApplication<br>StartAddr | string<br>No default                     | Start address of application specific MPU region hexadecimal value: StartAddr = 0x or application specific linker symbol: StartAddr = <appl_linker_start_symbol></appl_linker_start_symbol> |

| EndAddr            | OsApplication<br>EndAddr   | string<br>No default                     | End address of application specific MPU region hexadecimal value: EndAddr = 0x or application specific linker symbol: EndAddr = <appl_linker_end_symbol></appl_linker_end_symbol>           |

Value of StartAddr must always point to the first valid Byte in the specified memory area. Value of EndAddr must always point to the last valid Byte in the specified memory area. MpuRegion = Enable

```

{

StartAddr = 0x...;

EndAddr = 0x...;

};

```

The total number of used dynamic MPU regions depends on the application which has the most number of dynamic regions.

Example: if an application has 3 dynamic regions and other application has 5 dynamic regions then the total number of used dynamic MPU regions is 5.

#### 3.7 Event Attributes

Events in the MICROSAR OS operating system are always implemented as bits in bit fields. The user could use bit masks like '0x00000001' but to achieve portability between different MICROSAR OS implementation he should use event names which are mapped by the code generator to the defined bits. The MICROSAR OS RH850 implementation allows up to 32 events per task. The required size of the event masks is calculated automatically by the code generator. Possible event mask sizes are 8, 16 and 32 Bits.

# 3.8 Linker Include Files (SC3 and SC4)

The generated linker include files osdata.dld, osrom.dld, ossdata.dld, osstacks.dld and ostdata.dld are example files which can be used for mapping the OS and application data.

#### osdata.dld

Include file osdata.dld contains mapping for application and OS data. It should be included immediately after the default .data section.

#### osrom.dld

Include osrom.dld contains the mapping of initialized data which is copied by the start-up code from ROM to RAM area. It should be included at end of ROM section.

#### ossdata.dld

Include file ossdata.dld contains the mapping of application and OS data in SDA section. Due to limited number of MPU protection areas the SDA section of non-trusted application contain SDA and non-SDA data. This affects also the global shared data sections. This file must be included after the .sdata section.

#### osstacks.dld

Include file osstacks.dld contains the mapping of system stack, all task and all ISR stacks. This file should be included before application specific data sections.

#### ostdata.dld

Include file ostdata.dld contains mapping for application data in TDA section. This file should be included after the .zdata section.

# 4 System Generation

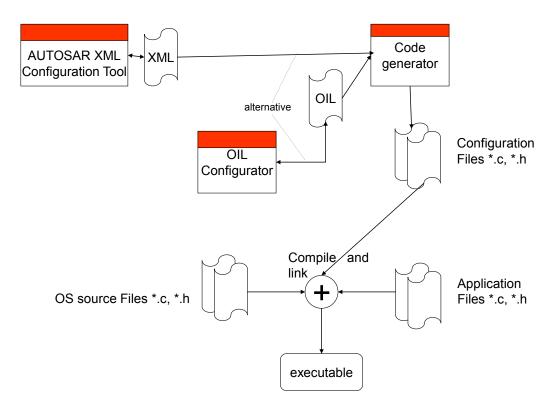

The system generation process is described in the document [3] which is common to all implementation. The following section describes the RH850 specific parts of the generating process.

Figure 4-1 System Generation

#### 4.1 Code Generator

The following files are generated by the code generator genRH850.exe

config.xml configuration information in XML-format

intvect c0.c interrupt vector tables

tcb.c applications and OS configuration

tcb.h

tcbpost.h

trustfct.h

trustfct.c trusted function stubs

osConfigBlock.c contains the configuration block

osStacks.h

osStacks.c stack definitions

Os MemMap.h contains definitions for MemMap usage

OILFileName.ort

OILFileName.htm

For SC3 and SC4 the following additional files are generated:

osdata.dld example linker include file for application data

osrom.dld example linker include file for application data initialization

ossdata.dld example linker include file for application data in SDA

osstacks.dld example linker include file for stacks

ostdata.dld example linker include file for application data in TDA

nontrustfct.h

For multicore systems the following additional files are generated:

ioc.h

Header for IOC related functions

• ioc.c IOC related functions

ccb.h

Header for multicore related attributes

ccb.c

Multicore related attributes

intvect\_c1.c

Interrupt vector tables for second core

The files tcb.c, tcb.h, trustfct.c, trustfct.h and nontrustfct.h are described in document [3].

The module intvect\_c<X>.c contains the interrupt vector tables for the Green Hills compiler, where X is the corresponding logical core ID.

Version: 1.11

The module *OILFileName*.ort is only generated if the configuration attribute *ORTIDebugSupport* is selected.

OILFileName.htm is containing information about the configuration settings.

# 5 Stack Handling

#### 5.1 Task Stacks

Each task runs on an own separate task stack. Tasks might share a stack as described in [3]. The PreTaskHook function always uses the system stack. The PostTaskHook function uses the system stack or in case of a task termination, it uses the task stack of the task that is terminated. Note that all task stacks must provide sufficient size for the maximum nesting level of ISR category 1. Therefore it is recommended to use ISR category 2 if possible.

The size of each task stack is determined by the configuration attribute StackSize of the configuration object TASK.

#### 5.2 ISR Stacks

An interrupt stack is defined for each interrupt priority level which is assigned to a CAT2 ISR. Each CAT2 ISR runs on the interrupt stack which is assigned to its priority level.

### 5.3 System Stack

The system stack is used by the dispatcher and by the hook wrappers.

### 5.4 Startup Stack

In function osStartOSasm the stack pointer is initialized to point to the system stack.

The system stack can be used as start-up stack.

The following linker symbol is provided for each core X to use the system stack as start-up stack:

osSystemStack EndAddr c<X>

#### 5.5 Stack Usage Size

The OS offers the possibility to determine the maximum stack usage of the OS stacks.

Please be aware, that the function stack usage determination for system stacks depends heavily on the positions in the code, where an ISR is interrupted by another ISR.

In the single stack model, the measured value for the system stack usage also depends heavily on the position in the code, where a basic task is preempted by another task. For this reason, it is extremely difficult, to find a conclusion for the worst case system stack usage from the measured stack usage.

NOTE: The API functions for determination of the stack usage are only available with the following configuration settings:

STACKMONITORING = TRUE StackUsageMeasurement = TRUE

# 5.5.1 Task Stack Usage

API function osGetStackUsage is described in [3].

# 5.5.2 System Stack Usage

The usage of the system stack since the start of the OS can be determined by using the function osGetSystemStackUsage.

Prototype:

```

typedef osuint16 osStackUsageType;

osStackUsageType osGetSystemStackUsage(void);

```

Argument: none

Return value: Maximum stack usage (bytes) of the system stack since StartOS().

# 5.5.3 ISR Stack Usage

The usage of the ISR stacks since the start of the OS can be determined by using the function osGetISRStackUsage.

Version: 1.11

Prototype:

```

typedef osuint16 osStackUsageType;

osStackUsageType osGetISRStackUsage(ISRType IsrIndex);

```

Argument: Index of the ISR

Return value: Maximum stack usage (bytes) of the ISR stack since StartOS().

# 6 Interrupt Handling

#### Note

This implementation supports interrupt handling according to the RH850 "expanded specifications" with a separate vector table for EIINT interrupts.

# 6.1 Interrupt Vectors

The code generator generates the interrupt vector tables. Therefore, all interrupt-service-routines have to be defined in the configuration. The interrupt vector tables are generated into the file intvect\_c<X>.c for the Green Hills compiler, where X is the corresponding logical core ID.

The interrupt vector tables are generated into three sections:

- ". osExceptionVectorTable\_c<X>" contains the core exception vector table

- ". osEIINTVectorTable\_c<X>" contains the EIINT exceptions vector table

- ".os\_text"

Contains the ISR prologue for CAT2 ISR wrappers

The length of the mentioned vector tables depends on the concrete derivative.

#### 6.1.1 Reset Vector

The user can specify an own reset vector. For this the user must configure a category 1 ISR which has the vector address 0x0, i.e. attribute ExceptionAddress=0x0.

If a category 1 ISR is configured for vector 0x0, this vector is generated as a jump to the specified address.

If this vector is not configured in the configuration, the vector 0x0 is generated as a jump to the startup code, delivered with the compiler.

Please note that all examples use the start-up module which is delivered with the compiler. For the Green Hills compiler this module is crt0.0

#### 6.1.2 Level Initialization

The user has to configure an interrupt priority level for all ISRs. MICROSAR OS initializes the appropriate interrupt control register with the level, configured by the user. The application is not allowed to change the interrupt priority level after StartOS is called.

# 6.2 Interrupt Level and Category

The RH850 controllers support interrupt levels. ISRs with lower level have priority over those with higher level. ISRs of lower level might therefore be nested into ISRs of higher level. Interrupt levels cannot be chosen independently from the category.

Because ISRs of category 2 can activate tasks, the exit code of a non-nested category 2 ISR has to check, if a task has been activated by the ISR itself or by any nested ISRs. If so, a task switch has to be set off. As category 1 ISRs have no such exit code, they must not be interrupted by category 2 ISRs. For this reason, MICROSAR OS checks, that all category 1 ISRs have lower or equal level value than the category 2 ISR with lowest level.

Note: Scalability class SC4 does not allow use of category 2 ISRs with priority level 0

### 6.3 Interrupt Category 1

For interrupts of category 1 no MICROSAR OS API functions can be used. Note that the category 1 ISR with highest priority value must have lower or equal priority value than the category 2 ISR with lowest priority value.

Example: if category 2 ISRs have priority levels 8, 10, 11 and 12 then category 1 cannot use priority levels 8 ... 15. Category 1 ISRs must then use priority levels 0 ... 7

Note: Scalability class SC4 does not allow use of category 1 ISRs for EIINT exceptions

# 6.3.1 Interrupt Processing in C

Using the Green Hills compiler, category 1 interrupt functions written in C must be implemented as described in the compiler manual:

For EIINT, you can use either of the following methods to declare a function as an interrupt routine:

- Place #pragma ghs interrupt immediately before the function.

- Prepend the interrupt keyword to the function definition.

Independently from the compiler, the user should not provide the interrupt vector number to the compiler, as the compiler would generate an interrupt vector in this case. Interrupt vector generation is always done by the operating system.

#### 6.3.2 Unhandled Exception Determination

If an unexpected interrupt occurs which is caused by an unused interrupts source then the ErrorHook and ShutdownHook are called and the system shutdown is requested.

The error type is reported to the application via error code E OS SYS ABORT.

If an unhandled core exception has occurred then the error reason is reported to the application via error number osdErrUEUnhandledCoreException. The global variable ossUnhandledCoreExceptionDetail contains the content of register FEIC and the global variable ossUnhandledExceptionDetail contains the offset of the core exception.

If an unhandled EIINT exception has occurred then the error reason is reported to the application via error number osdErrUEUnhandledEIINTException. The global variable ossUnhandledEIINTDetail contains the content of register EIIC and the global variable ossUnhandledExceptionDetail contains the index of the EIINT exception.

# 6.4 Interrupt Category 2

# 6.4.1 Interrupt Entry

The entry code of category 2 ISRs is automatically generated by MICROSAR OS. This code stores the GPR registers onto stack and calls the CAT2 ISR wrapper.

**SC1 and SC3**: The CAT2 ISR wrapper clears the global interrupt disable flag if the attribute *EnableNesting* is set for this ISR before calling the corresponding ISR function. If this attribute is not set then the CAT2 ISR wrapper does not clear the global interrupt disable flag.

**SC4:** The CAT2 ISR wrapper sets register PMR to system level and clears the global interrupt disable flag if the attribute *EnableNesting* is set for this ISR before calling the corresponding ISR function. If this attribute is not set then the CAT2 ISR wrapper sets register PMR to task level and then clears the global interrupt disable.

# 6.4.2 Interrupt Exit

The necessary return from exception is implemented in the CAT2 ISR wrapper exit code. The application is not allowed to issue a return from exception instruction.

#### 6.4.3 CAT2 ISR Function

For category 2 ISRs, the user has to use the ISR-macro provided by MICROSAR OS. The name which is given to this macro must be identical to the name in the configuration.

```

ISR( myISR )

{

... /* ISR function body */

}

```

# 6.5 Disabling Interrupts

#### Caution

It is not allowed to disable interrupts longer than the tick time <code>SECONDSPERTICK</code> of the hardware counter (timer). If interrupts are disabled longer than the tick time the alarm management could be handled wrong. This error is *not* detected by the operating system.

Only when compiling the operating system with the extended status additional error checking is performed.

# 7 MPU Handling (SC3 and SC4)

# 7.1 MPU Region Usage

MPU region 0 is used for stack area protection and all other MPU regions can be configured by the user to be static or dynamic (reprogrammed).

The total number of available MPU regions depends on the derivative group:

| Derivative group | Number of MPU regions (per Core) |

|------------------|----------------------------------|

| D1L and D1M      | 12                               |

| E1L and E1M      | 12                               |

| E1x-FCC2         | 16                               |

| F1H and F1M      | 16                               |

| F1L              | 4                                |

| P1M              | 12                               |

# 7.1.1 MPU Region 0

MPU region 0 is used for stack area protection and cannot be configured by the user. It is always reprogrammed by the OS when the context is switched. Therefore trusted and non-trusted applications can only write to the task and ISR stacks which belong to the application.

#### 7.1.2 Static MPU Regions

If a MPU region shall be static, i.e. it is only initialized in StartOS and not reprogrammed when context is switched then it has to be configured in the OS specific section. The region number is not required. The OS generator assigns a region number for each configured static MPU region.

The user must specify start address, end address and region attributes of the memory area. Furthermore, for Multicore OS the core assignment has to be specified.

If a MPU region is configured to be static then it is initialized in StartOS with settings from the configuration block.

# 7.1.3 Dynamic MPU Regions

If a MPU region shall be dynamic, i.e. it is always reprogrammed when context is switched then it has to be configured in each corresponding non-trusted application section. The region number is not required. The OS generator assigns a region number for each configured dynamic MPU region. Trusted applications cannot be configured with MPU regions.

The user must specify start and end address of the memory area. The region attributes are configured by the OS.

If a MPU region is configured to be dynamic then it is initialized in StartOS to be unused. After StartOS it is always reprogrammed when a non-trusted application is started or terminated.

Non-trusted applications can have different number of MPU regions. The total number of reprogrammed MPU regions depends on the application which has the most dynamic regions on the corresponding core. Example: If a system has 2 non-trusted applications on the same core, one application configured with 2 MPU regions and the other application configured with 3 MPU regions, then the total number of dynamic MPU regions is 3. During runtime when context is switched then always 3 MPU regions are reprogrammed.

Non-trusted application Appl1:

- MPU region 1 used

- MPU region 2 used

Non-trusted application Appl2:

- MPU region 1 used

- MPU region 2 used

- MPU region 3 used

When application Appl1 is started then MPU regions 1 and 2 are reprogrammed with application specific settings and MPU region 3 is set to unused.

When application Appl2 is started then MPU regions 1, 2 and 3 are reprogrammed with application specific settings.

# 8 RH850 Peripherals

# 8.1 Supported System Timer

MICROSAR OS RH850 uses the timer unit OSTM as driver for a configured hardware counter (see 3.4). The corresponding interrupt channel depends on the derivative group:

| Derivative group | Used Interrupt Channel                   | Used Hardware Unit                         |

|------------------|------------------------------------------|--------------------------------------------|

| D1L / D1M        | 125                                      | OSTM0                                      |

| E1L / E1M        | 25                                       | OSTM0                                      |

| E1x-FCC2         | 25<br>26 for second core (Multicore OS)  | OSTM0 OSTM1 for second core (Multicore OS) |

| F1M              | 84                                       | OSTM0                                      |

| F1H              | 84<br>314 for second core (Multicore OS) | OSTM0 OSTM5 for second core (Multicore OS) |

| F1L              | 76                                       | OSTM0                                      |

| P1M              | 74                                       | OSTM0                                      |

Table 3 RH850 driver for hardware counter

# 8.2 Supported Time Monitoring Timer

MICROSAR OS RH850 uses the timer unit TAUJ0 for SC4 timing protection:

| Derivative group | Used Interrupt Channels         | Used Hardware Unit |

|------------------|---------------------------------|--------------------|

| D1L / D1M        | 121, 122, 123                   | TAUJ0              |

| E1L / E1M        | Timing Protection not supported | -                  |

| F1H / F1M        | 80, 81, 82                      | TAUJ0              |

| F1L              | 72, 73, 74                      | TAUJ0              |

| P1M              | 133, 134, 135                   | TAUJ0              |

Table 4 RH850 timer units for timing protection

### 8.3 Initialization

The OS initializes the interrupt controller INTC before the StartupHook is called.

Register SCBASE and SCCFG are initialized to use the OS syscall table (SC3 and SC4).

The OS initializes the timer OSTM after the StartupHook is called.

In case of SC3 and SC4, the OS initializes the memory protection unit MPU before the StartupHook is called.

In case of SC4, the OS initializes the timer unit TAUJ0 before the StartupHook is called.

# 9 Implementation Specifics

#### 9.1 API Functions

### 9.1.1 DisableAllInterrupts

**SC1** and **SC3**: The function *DisableAllInterrupts* disables all interrupts. This is achieved by setting the ID-Bit in register PSW. The old value of the ID-Bit is stored for later restore.

**SC4:** The function *DisableAllInterrupts* disables interrupts up to priority level 1. Interrupts with priority level 0 stay enabled. This is performed by setting bits 1...15 in register PMR. The old value of the register is stored for later restore. Interrupts of priority level 0 stay enabled so that timing protection exceptions can still occur.

Remark: Nested calls are not possible.

### 9.1.2 EnableAllInterrupts

**SC1 and SC3:** The function *EnableAllInterrupts* restores the content of the ID-Bit which was stored by *DisableAllInterrupts*.

**SC4:** The function *EnableAllInterrupts* restores the content of register PMR which was stored by *DisableAllInterrupts*.

Remark: Nested calls are not possible.

# 9.1.3 SuspendAllInterrupts

**SC1** and **SC3**: The function *SuspendAllInterrupts* disables all interrupts. This is achieved by setting the ID-Bit in register PSW. The old value of the ID-Bit is stored for later restore.

**SC4:** The function *SuspendAllInterrupts* disables interrupts up to priority level 1. Interrupts with priority level 0 stay enabled. This is performed by setting bits 1...15 in register PMR. The old value of the register is stored for later restore. Interrupts of priority level 0 stay enabled so that timing protection exceptions can still occur.

Remark: Nested calls are possible.

#### 9.1.4 ResumeAllInterrupts

**SC1 and SC3:** The function *ResumeAllInterrupts* restores the content of the ID-Bit which was stored by *SuspendAllInterrupts*.

**SC4:** The function *ResumeAllInterrupts* restores the content of register PMR which was stored by *SuspendAllInterrupts*.

Remark: Nested calls are possible.

#### 9.1.5 SuspendOSInterrupts

The function *SuspendOSInterrupts* disables all category 2 interrupts. This is achieved by setting the PMR register to system level (highest interrupt priority of all category 2 interrupts). The old value of the PMR register is stored for later restore.

**Remark**: Nested calls are possible.

### 9.1.6 ResumeOSInterrupts

The function *ResumeOSInterrupts* restores the content of register PMR which was stored by *SuspendOSInterrupts*.

Remark: Nested calls are possible.

#### Note

If OS API functions are used before StartOS then osInitialize must be called before any OS API function is called. If SC3 or SC4 is used, then also osInitINTC must be called before StartOS.

#### 9.1.7 GetResource

MICROSAR OS RH850 SC3/SC4 does not support the extension of the resource concept for interrupt levels.

#### 9.1.8 ReleaseResource

MICROSAR OS RH850 SC3/SC4 does not support the extension of the resource concept for interrupt levels.

#### 9.1.9 GetAlarmBase

MICROSAR OS RH850 SC3/SC4 does not support API function GetAlarmBase.

#### 9.1.10 oslnitialize

Function osInitialize is used for initializing OS global variables which are used by osDispatcher and interrupt handling API. It is called by the OS in StartOS.

Prototype: void oslnitialize(void)

#### 9.1.11 oslnitINTC

Function osInitINTC initializes the interrupt controller INTC and some core registers for the corresponding core X:

- EBASE = &osExceptionVectorTable c<X>

- INTBP = &osEIINTVectorTable c<X>

- INTCFG = 0

- SCBP = &osSysCallTable c<X> (SC3 and SC4)

- SCCFG = osdNumberOfSysCallFunctions (SC3 and SC4)

- set table mode and priority level for each configured EIINT interrupt source assigned to core X

Version: 1.11

osInitINTC is called by the OS in StartOS.

Prototype: void osInitINTC(void)

# 9.2 Peripheral Region API

In a safety application there is the need to access peripheral components from QM software (non-trusted).

For QM software, which runs in restricted mode (e.g. user mode) the peripheral access must be granted by the MPU. Sometimes there are peripheral registers which cannot be written at all in restricted mode.

Therefore the OS offers the concept of the peripheral region API.

The peripheral regions are defined in the configuration. Access rights are also configured on application level.

With an API any Software (also non trusted) is capable to write to peripheral registers even if the access is not granted by the MPU.

#### 9.2.1.1 Read Functions

There are three reading functions.

#

# **Functional Description**

- > reads either an 8 bit, or a 16 bit or a 32 bit value from "address"

- > The function performs accessing checks (whether the caller has accessing rights to the peripheral region and whether the address to be read from is within the configured range of the peripheral region)

- > The error hook is raised in case of an error

- A shutdown is not issued in case of an error

#### **Particularities and Limitations**

> These functions may not be called from OS hooks

### Call context

- > These functions may be called from Task context

- > These functions may be called from category 2 ISR context

- > These functions can be called with interrupts enabled or with interrupts disabled

#### 9.2.1.2 Write Functions

There are three writing functions.

### Prototype

void osWritePeripheral8 ( osuint16 area, osuint32 address, osuint8 value)

void osWritePeripheral16( osuint16 area, osuint32 address, osuint16 value)

void osWritePeripheral32( osuint16 area, osuint32 address, osuint32 value)

| Parameter |                                                   |

|-----------|---------------------------------------------------|

| area      | Identifier of peripheral regions to the read from |

| address   | Address to write to                               |

| value     | Value to be written                               |

#### Return code

None

# **Functional Description**

- > Writes to either an 8 bit, or a 16 bit or a 32 bit value

- > The function performs accessing checks (whether the caller has accessing rights to the peripheral region and whether the address to be read from is within the configured range of the peripheral region)

- > The error hook is raised in case of an error

- > A shutdown is not issued in case of an error

#### **Particularities and Limitations**

> These functions may not be called from OS hooks

#### Call context

- > These functions may be called from Task context

- > These functions may be called from category 2 ISR context

- > These functions can be called with interrupts enabled or with interrupts disabled

©2016, Vector Informatik GmbH Version: 1.11 32 / 58

# 9.2.1.3 Modify Functions

There are three modifying functions.

# **Prototype**

void osModifyPeripheral8 ( osuint16 area, osuint32 address, osuint8 clearmask, osuint8 setmask)

void osModifyPeripheral16( osuint16 area, osuint32 address, osuint16 clearmask, osuint16 setmask)

void osModifyPeripheral32( osuint16 area, osuint32 address, osuint32 clearmask, osuint32 setmask)

| Parameter |                                                   |

|-----------|---------------------------------------------------|

| area      | Identifier of peripheral regions to the read from |

| address   | Address to be modified                            |

| clearmask | Bitmask which is bitwise "ANDed" to "address"     |

| setmask   | Bitmask which is bitwise "ORed" to "address"      |

#### Return code

None

#### **Functional Description**

- > The function performs accessing checks (whether the caller has accessing rights to the peripheral region and whether the address to be read from is within the configured range of the peripheral region)

- > The error hook is raised in case of an error

- > A shutdown is not issued in case of an error

- > After the access checks has passed first the "clearmask" is ANDed to "address" and afterwards the "setmask" is ORed to it.

#### **Particularities and Limitations**

> These functions may not be called from OS hooks

#### Call context

- > These functions may be called from Task context

- > These functions may be called from category 2 ISR context

- > These functions can be called with interrupts enabled or with interrupts disabled

©2016, Vector Informatik GmbH Version: 1.11 33 / 58

# 9.3 Peripheral Interrupt API Functions (SC3 and SC4)

The OS provides functions which can be used to perform write access to the interrupt controller INTC control registers in user mode.

If read access to SFR registers is enabled in user mode then the following macros can be used to read from interrupt controller INTC registers.

```

#define osReadICR8(addr) (*((osuint8*)(addr)))

#define osReadICR16(addr) (*((osuint16*)(addr)))

```

This chapter describes API functions which can be used to access the interrupt control registers within the corresponding address range:

| Derivative group | Address range                           |

|------------------|-----------------------------------------|

| D1L/D1M          | FFFE EA00 - FFFE EA3E (EICO to EIC31)   |

|                  | FFFF B040 - FFFF B1FE (EIC32 to EIC255) |

| E1L/E1M          | FFFE EA00 - FFFE EA3E (EICO to EIC31)   |

|                  | FFFF B040 - FFFF B3FE (EIC32 to EIC511) |

| E1x-Fcc2         | FFFE EA00 - FFFE EA3E (EICO to EIC31)   |

|                  | FFFF B040 - FFFF B3FE (EIC32 to EIC511) |

| F1H              | FFFE EA00 - FFFE EA3E (EICO to EIC31)   |

|                  | FFFF B040 - FFFF B2BC (EIC32 to EIC350) |

| F1L              | FFFF 9000 - FFFF 903E (EICO- EIC31)     |

|                  | FFFF A040 - FFFF A232 (EIC32- EIC281)   |

| F1M              | FFFE EA00 - FFFE EA3E (EICO to EIC31)   |

|                  | FFFF B040 - FFFF B25C (EIC32 to EIC297) |

| P1M              | FFFE EA00 - FFFE EA3E (EICO to EIC31)   |

|                  | FFFF B040 - FFFF B2FE (EIC32 to EIC383) |

# 9.3.1 Write to Interrupt Control Register

Writing 1 or 2 Byte to the interrupt controller INTC control register is achieved by osWriteICR8/osWriteICR16 and osWriteICRxLo/ osWriteICRxHi/ osWriteICRx16:

# osWriteICR8

This function writes 1 Byte at specified destination address. Before writing the address parameter is checked to be in valid range.

| Prototype                                            |                                            |

|------------------------------------------------------|--------------------------------------------|

| <pre>void osWriteICR8(uint32 addr, uint8 val);</pre> |                                            |

| Parameter                                            |                                            |

| addr                                                 | destination address                        |

| val                                                  | value to be written at destination address |

| Return Code                                          |                                            |